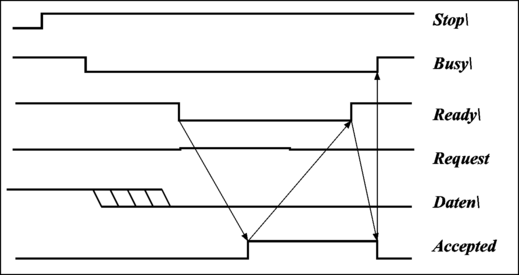

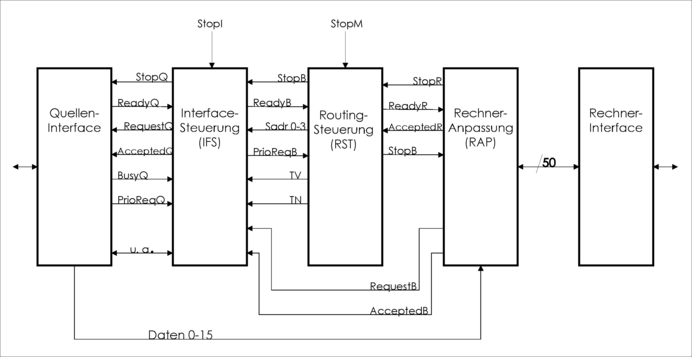

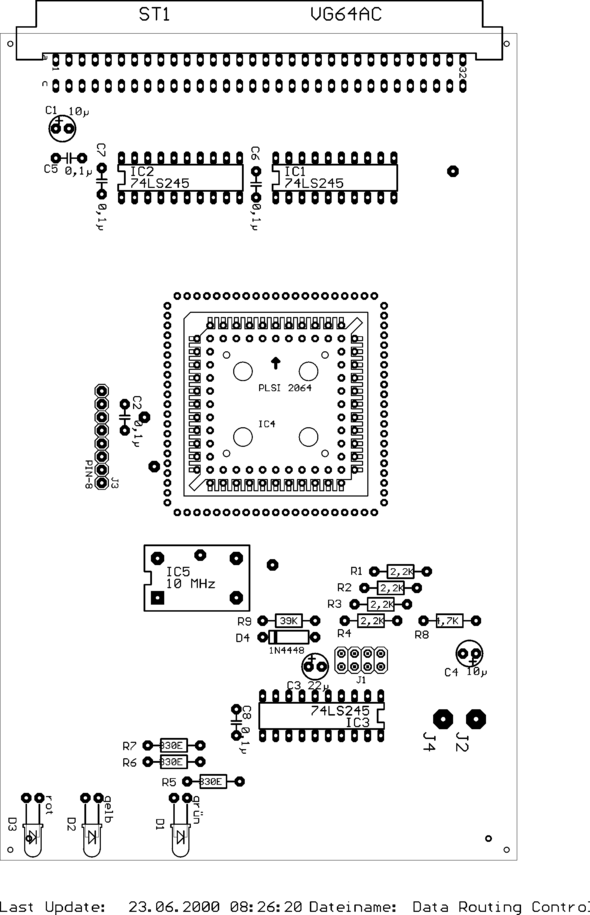

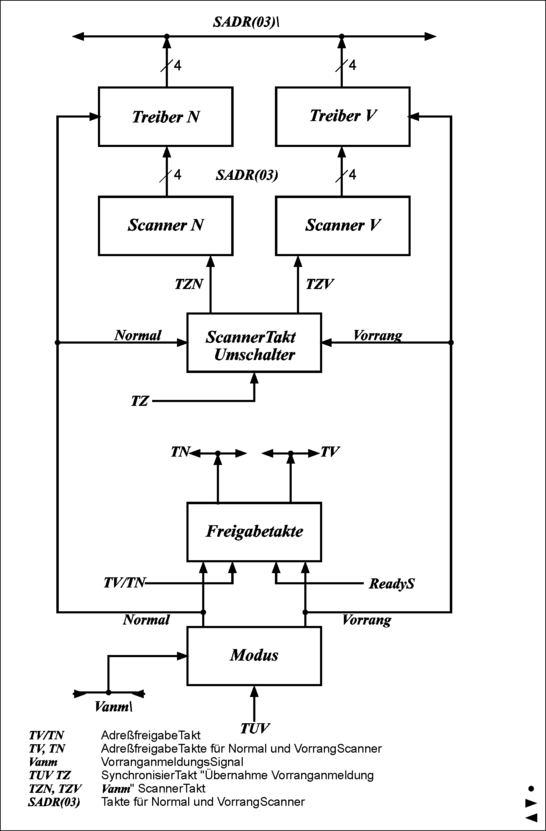

Abb. 2.1.0.1 Dateneingabe mit dem Data-Routing-System

(Multiplexer für 16-Bit Dateneingabe)

März 1995 K. Huber, Strahlenzentrum Univ. Gießen

Version 11.Oct.2024

| • Einleitung | ||

| • Aufbau und Funktion | ||

| • Standard-Interface-Karten | ||

| • Spezielle Interface-Karten | ||

| • Zählratenstatistik | ||

| • Technische Details | ||

| • Oldies |

Nächste: Aufbau und Funktion, Nach oben: Top [Inhalt]

Zur Datenerfassung und Experimentsteuerung existieren zwei verschiedene Rechner-Interfaces, das Data-Routing und das Control-Routing, so genannt nach den Aufgaben, zu denen sie im Wesentlichen eingesetzt werden:

Die vorliegende Funktionsbeschreibung befasst sich

ausschließlich mit dem Data-Routing. Es wird im folgenden oft

abgekürzt als Routing bezeichnet.

Für das Control-Routing existiert eine eigene Beschreibung.

Das Kapitel Aufbau und Funktion gibt einen Überblick über den Aufbau das Data-Routing.

Das Kapitel Standardkomponenten enthält die Aufgabenbeschreibungen und Bedienungsanleitungen der Standardkarten des Routing.

Das Kapitel Standard-Interface-Karten enthält die Aufgabenbeschreibungen und Bedienungsanleitungen der Routing-Karten, die allgemein bei Experimenten zum Einsatz kommen.

Das Kapitel Spezielle Interface-Karten enthält eine Aufstellung der Routing-Karten, die für einzelne Experimente entwickelt wurden. Ihre Beschreibung findet man i.a. in den Unterlagen der Experimente, bei denen sie eingesetzt werden.

Das Kapitel Technische Details gibt technische Detail-Informationen über die Komponenten und deren Schnittstellen.

Im Kapitel Oldies sind überholte Beschreibungen gesammelt.

Vorige: Einleitung, Nach oben: Top [Inhalt]

| • Aufbau des Routing | ||

| • Überrahmen |

Nächste: Ueberrahmen, Nach oben: Aufbau und Funktion [Inhalt]

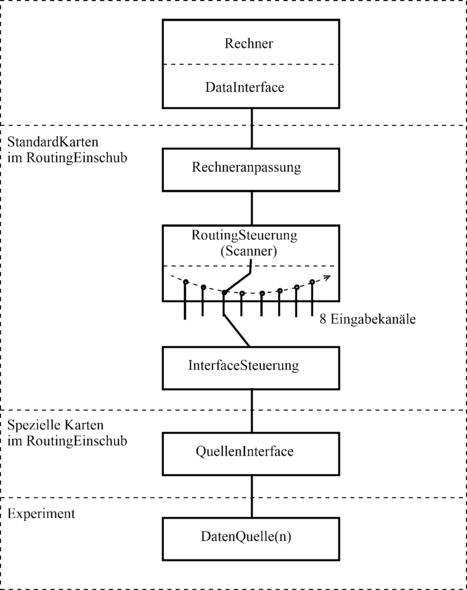

Abb. 2.1.0.1 Dateneingabe mit dem Data-Routing-System

Vorige: Aufbau des Routing, Nach oben: Aufbau und Funktion [Inhalt]

Das Data-Routing ist in einem 19"-Überrahmen untergebracht

mit 20 Steckplätzen für Europakarten (Abb. 2.2.0.1).

Es wird der

gleiche Überrahmen wie für das Control-Routing verwendet. In

Ausnahmefällen können Data-Routing und Control-Routing im gleichen

Überrahmen untergebracht werden, wenn die Bus-Verdrahtung in

der Mitte durchtrennt wird und für die zweite Hälfte ein

Bus-Abschluss nachgerüstet wird.

Die Routing Back-Plane enthält 42 allgemeine Bus-Leitungen für

die Routing-Steuerung und 11 Privat-Bus-Leitungen zur

Kommunikation benachbarter Karten.

Außer der Spannungsversorgung sind alle Schaltungskomponenten

auf steckbaren Karten untergebracht.

Als Steckverbindung zum Routing-Bus werden 64-polige VG-Stecker verwendet. Die Anschlüsse der VG-Leisten sind im Überrahmen zum Teil als durchgehender Bus verdrahtet (allg. Bus: 1a,1c,...,21c) und zu einem anderen Teil bestehen Verbindungen zu benachbarten Steckerleisten (Privat-Bus: 22a/c,...,32a/c) (Siehe Routing-Bus.). Ferner ist für jede Leiste von links beginnend eine Steckplatzkodierung von 0-7 verdrahtet, wobei jedoch jeweils zwei benachbarte Leisten die gleiche Kodierung haben. Die vier überbleibenden Steckplätze am rechten Ende erhalten alle die Kodierung 7. Sie sind vorzugsweise für die Rechner-Anpassung und Routing-Steuerung zu benutzen, da der Bus-Abschluss sich am linken Ende des Überrahmens befindet. Am äußersten rechten Ende ist die Netzkarte mit Netzschalter und Betriebsspannungsanzeigen fest installiert.

Die Frontplattenbreite für eine Steckkarte ist üblicherweise 20 mm, es stehen jedoch auch 40 und 50 mm Frontplatten zur Verfügung.

Achtung:

Es wird dringend empfohlen, die Frontplatten der Steckkarten

mit dem Überrahmen zu verschrauben zur Vermeidung von

Betriebsstörungen. Bitte die Schrauben nicht gewaltsam

anziehen, da dies zur Zerstörung der Gewinde im Überrahmen

führt. Schrauben von min. 10mm Länge verwenden, sonst besteht

ebenfalls die Gefahr der Zerstörung der Gewinde.

Abb. 2.2.0.1 Routing-Überrahmen

Steckplatz

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20

+--+--+--+--+--+--+--+--+--+--+--+--+--+--+--+--+--+--+--+--+--+

| | | | | | | | | | | | | | | | | | |RS|RA|SV|

| | | | | | | | | | | | | | | | | | | | | |

| | | | | | | | | | | | | | | | | | | | | |

| | | | | | | | | | | | | | | | | | | | | |

+--+--+--+--+--+--+--+--+--+--+--+--+--+--+--+--+--+--+--+--+--+

0 0 1 1 2 2 3 3 4 4 5 5 6 6 7 7 7 7 7 7

Steckplatzkodierung

RS = Routingsteuerung

RA = Rechneranpassung

SV = Spannungsversorgung

Nächste: Rechneranpassung (RAP) [Inhalt]

| • Aufgabe | ||

| • Bedienungselemente, Anzeigen |

Nächste: Bedienungselemente (RST), Nach oben: Routing-Steuerung (RST) [Inhalt]

Die Routing-Steuerung koordiniert die Eingabe der Daten von den bis zu acht anschließbaren Eingabekanälen. Ein Eingabekanal besteht aus den drei funktionellen Gruppen:

Siehe Aufbau des Routing.

Siehe Komponenten und Schnittstellen.

Die Routing-Steuerung ist mit zwei alternativ laufenden Scannern unterschiedlicher Priorität ausgestattet, mit denen die Eingabekanäle abgefragt werden. Dadurch besteht die Möglichkeit, einen oder mehrere Eingabekanäle mit Vorrang vor den anderen abfragen zu lassen. Dazu müssen diese Eingabekanäle einen Vorrangwunsch bei der Routing-Steuerung anmelden, sobald sie bereit sind ein Datenwort zu übertragen. Der jeweils ruhende Scanner behält seine Position bei, so dass er an der unterbrochenen Stelle weiterlaufen kann.

Um verkürzte Scanner-Umläufe zu ermöglichen, sind die Scanner-Adressen in vier Gruppen zusammengefasst, die in Einer-, Zweier- oder Vierer-Kombinationen durch einen Jumper aktiviert werden können. Die Scanner-Adressen werden stets in einer Reihenfolge durchlaufen in der sich höchstens 2 Bits gleichzeitig ändern, um Störungen auf dem Routing-Bus zu minimieren (Siehe Routing-Steuerung.).

Es ist zu beachten, dass die verschiedenen Eingabekanäle von der Routing-Steuerung nicht nach einem ’first in - first out’ Verfahren bearbeitet werden, sondern durch einen Scanner reihum abgefragt werden. Dies kann zur Folge haben, dass die einzelnen Eingabekanäle nicht in der Reihenfolge zum Rechner übertragen werden, in der sie zur Übertragung bereit waren. Die damit zusammenhängenden Probleme der Verkoppelung von Datenquellen z.B. bei Koinzidenzexperimenten sind jedoch berücksichtigt (Siehe Kopplungskarte (KPL).).

Ein Stop der Routing-Steuerung kann vom Rechner her erfolgen oder über einen Schalter auf der Frontplatte. Beide bewirken ein Anhalten der Daten-Scanner. Ferner wird der Stop den Eingabekanälen mitgeteilt und über die Interface-Steuerung den Datenquellen.

Die Routing-Steuerung arbeitet eng mit der Rechneranpassungs-Karte zusammen und steckt deshalb direkt links neben ihr.

Vorige: Aufgabe (RST), Nach oben: Routing-Steuerung (RST) [Inhalt]

Schalter: Run/Stop

In Stellung Stop wird die Abfrage der Eingabekanäle angehalten

durch Stoppen des Daten-Scanners. An die Eingabekanäle geht

ein Stopsignal. Der Schalter ist disjunktiv (ODER) verknüpft

mit dem Stop vom Rechner.

Anzeige: Run

Wenn weder vom Rechner noch durch den Schalter Run/Stop ein

Stop erfolgt, d.h. die Routing-Steuerung läuft, so leuchtet

die Anzeige Run.

Anzeige: Ready

Solange die Routing-Steuerung das Data Ready (ReadyB) eines

Eingabekanals bearbeitet, leuchtet die Anzeige Ready.

Anzeige: Vorrang

Solange die Routing-Steuerung im Vorrangmodus arbeitet,

leuchtet die Anzeige Vorrang.

Jumper: Group 0 1 2 3

Selektion von Scanner-Gruppen 0 1 2 3.

Erlaubte Kombinationen von Gruppen sind

0, 1, 2, 3, 0-1, 0-2, 1-3, 2-3, 0-1-3-2.

Bei unzulässigen Kombinationen, und falls kein Jumper gesetzt ist,

wird 0-1-3-2 ausgeführt.

Nächste: Interface-Steuerung (IFS), Vorige: Routing-Steuerung (RST) [Inhalt]

| • Aufgabe | ||

| • Bedienungselemente, Anzeigen |

Nächste: Bedienungselemente (RAP), Nach oben: Rechneranpassung (RAP) [Inhalt]

Die Rechneranpassungs-Karte hat die Aufgabe aus den Daten- und Kennungsbits auf dem Bus ein Datenwort zusammenzustellen, es in Fifos zwischenzuspeichern und dann an den Rechner zu übertragen. Darüberhinaus enthält die Rechneranpassungs-Karte Sender, Empfänger und eventuell Pegelwandler für die Dialog-Signale zwischen dem Rechner und dem Routing.

Die Verbindung zum Rechner erfolgt über ein max. 40m langes 50-poliges Flachbandkabel. Kurze Kabellängen sind zu bevorzugen da die Länge in die Übertragungsgeschwindigkeit eingeht und kürzere Kabel störungssicherer sind.

Für Testzwecke am Routing kann das 50-polige Verbindungskabel zum Rechner abgezogen werden. Die Rechneranpassung nimmt dann dem Routing die Daten mit höchstmöglicher Geschwindigkeit ab (und wirft sie weg).

Bisher wurden drei Anpassungen an verschiedene Host-Rechner realisiert:

Aktuell ist die VME - Anpassung, die zusammen mit dem rechnerseitigen

Interface eine Schnittstelle zu dem Industry Pack Standard darstellt.

Für diesen IP-Standard werden Carrier-Boards für eine Anzahl

weiterer Plattformen (z.B. PC) angeboten, so dass ein Anschluss

des Data-Routing an einen anderen Rechnertyp ohne großen

Aufwand möglich ist.

Die TR86- und PDP11-Anpassungen wurden inzwischen ausgemustert.

Ihre Beschreibung finden Sie bei den ’Oldies’.

Die sogn. Silena-Änderung wurde in die aktuelle VME-Rechneranpassung nicht mit übernommen, sondern es wird vorausgesetzt, dass eine entsprechende Änderung auf allen Silena-Interface-Karten vorgenommen ist.

Die Rechneranpassungs-Karte arbeitet sehr eng mit der Routing-Steuerung zusammen und steckt deshalb direkt rechts neben ihr.

Vorige: Aufgabe (RAP), Nach oben: Rechneranpassung (RAP) [Inhalt]

Die Rechneranpassungskarte besitzt keine Bedienungselemente. Auf dem Board (von außen nicht sichtbar) befindet sich eine grüne LED zum Anzeigen einer aktiven Verbindung mit dem Rechner und eine rote LED zum Anzeigen eines Fifo-Errors.

Nächste: Kopplungskarte (KPL), Vorige: Rechneranpassung (RAP) [Inhalt]

| • Aufgabe | ||

| • Bedienungselemente, Anzeigen |

Nächste: Bedienungselemente (IFS), Nach oben: Interface-Steuerung (IFS) [Inhalt]

Die Interface-Steuerung stellt eine standardisierte Karte zwischen der Routing-Steuerung und den Datenquellen dar. Im Zusammenspiel mit der Routing-Steuerung wickelt sie die Routing-Logik ab und bietet den Datenquellen eine bequeme Schnittstelle, die den Anschluss von Datenquellen wesentlich erleichtert. Ferner ist sie zur Lifetime-Messung, zur Eingabe von Daten im Vorrangmodus und zur Eingabe von gekoppelten Daten (Koinzidenz-Experimente) vorbereitet. Zum Anschluss von Datenquellen sind, je nach Komplexität der Aufgabe, noch ein oder mehrere Quellen-Interface-Karten notwendig, die im einfachsten Falle nur Pegelwandler und Bus-Leitungstreiber enthalten.

Zur Verständigung mit den Quellen-Interface-Karten baut die IFS-Karte nach rechts einen Privat-Bus (IFS-Bus) auf. Die Quellen-Interface-Karten müssen deshalb stets rechts von der IFS-Karte stecken. Die Frontplatten der so miteinander kommunizierenden Karten müssen fest mit dem Überrahmen verschraubt sein, um eine gute Masseverbindung von den Karten zur Frontplatte herzustellen. Fehlt die Verschraubung so kann dies zu schwerwiegenden Betriebsstörungen führen, weil die Karten wie die Kondensatorplatten eines gedämpften Oszillators gegeneinander schwingen.

Es existieren zwei Varianten (IFS und IFS1) der Interface-Steuerung, die sich in ihren Funktionen nicht wesentlich unterscheiden. Bei der älteren (IFS) sind die Konfigurationsbrücken als Lötbrücken (statt Steckbrücken) ausgeführt und unbeschriftet und auf der Frontplatte fehlt die Anzeige für den Vorrangbetriebsmodus.

Vorige: Aufgabe (IFS), Nach oben: Interface-Steuerung (IFS) [Inhalt]

Stop/Run/LFT (Schalter)

Schalter für den Betriebsmodus.

LFTQ = BusyQ\ * GateQ(Option) * (K2 * LFTK\)\

Die Option wird eingeschaltet durch Stecken der Brücke LFT\= By+G statt By. Immer, wenn dieses Signal LFTQ ansteht wird der interne Lifetime-Zähler mit 1MHz Takt hochgezählt. Sobald auf diese Weise 1s bzw. 0.1s (Brücke: 1s/0.1s) Lifetime zusammengekommen sind, wird ein Datenwort übertragen, das zur Unterscheidung neben der normalen Quellenkennung noch das Lifetime-Bit (Siehe »Rechneranpassung«.) gesetzt hat. Alle Daten-Bits sind null. Diese Funktion der IFS-Karte erlaubt totzeitkorrigierte Messungen.

Da die Totzeitsignale intern mit einem 1MHz-Takt abgefragt werden, kann es zu Fehlmessungen der Lifetime kommen, wenn die Totzeitsignale phasensynchron mit dem internen 1MHz-Takt und in der Größenordnung der Taktperiode sind. Für völlig vom internen Takt unabhängige Totzeitsignale sollten hingegen vom Schaltungsentwurf her auch kürzere als 1us richtig verarbeitet werden, auf einer statistischen Basis, in dem sie mal einen Takt durchlassen und mal nicht (hab’ dies aber bis jetzt noch nicht überprüft!).

Achtung: Aus Kostengründen sind nicht alle IFS-Karten mit den für die LFT-Messung notwendigen Bausteinen (SAJ141) bestückt.

Frei/K1/K2 (Schalter)

Sollen mehrere Datenquellen gekoppelt übertragen werden (z.B.

bei Koinzidenz-Experimenten), so wird über diesen Schalter

entschieden in welcher Weise die zugehörige Datenquelle an der

Kopplung teilnimmt. Detailierte Information ist der

Beschreibung der Kopplungskarte zu entnehmen (Siehe Kopplungskarte (KPL).).

GateQ: (TTL-Eingang)

Über diesen Eingang kann die Datenquelle auf- und

zugegatet werden. Bei Betrieb im Modus K2 erfolgt eine

Verknüpfung mit dem Signal GateK und dem Kopplungssignal

(siehe GateK).

High oder offener Eingang: Gate offen

GateK: (TTL-Eingang)

Über diesen Eingang kann, um spezielle Zeitbedingungen zu

realisieren, das Kopplungssignal (siehe Modus K1, K2)

extern zugeführt werden. Es wird mit dem internen

Kopplungssignal (KoppK), das von der Kopplungskarte

geliefert wird, konjunktiv (UND) verknüpft. Für den

Kopplungsmodus K2 wird das Ergebnis noch mit dem Eingang

GateQ konjunktiv verknüpft und als Gate-Signal

(GateSQ) an die Datenquelle übergeben.

High oder offener Eingang: Gate offen

GateSQ= GateQ * (K2\ + K2 * KoppK * GateK)

Out: (TTL-Ausgang)

Je nach Konfiguration der IFS-Karte (Steckbrücke: Gate/By)

kann über diesen Ausgang das Busy-Signal der Datenquelle

oder das Gate-Signal für die Datenquelle beobachtet

werden.

High: Quelle Busy/Gate offen

Run bzw. R/S: (LED-Anzeige)

Run/Stop-Anzeige

LED leuchtet: IFS-Karte läuft

B bzw. By: (LED-Anzeige)

Busy Anzeige

LED leuchtet: Datenquelle meldet Busy

VR: (LED-Anzeige; nur IFS1)

Vorranganzeige

LED leuchtet: Die Datenquelle arbeitet im Vorrangmodus

4 2 1: (LED-Anzeige)

Anzeige der Steckplatzadresse.

Zur Unterscheidung der verschiedenen Datenquellen wird dem

Datenwort die Steckplatzadresse als Quellenkennung

mitgegeben. Da im allgemeinen beim Start eines

Messprogrammes die Quellenkennung angegeben werden muss,

wird die Steckplatzadresse von der IFS-Karte angezeigt.

LED leuchtet: Bit der angegenbenen Wertigkeit ist gesetzt.

1s / 0.1s: (Jumper)

Zeitbasis für die Übertragung des Lifetime-Datenwortes (s.o.).

Out = Gate / Busy: (Jumper)

Beschaltung der ’Out’ BNC-Buchse mit Gate- oder Busy-Signal (s.o.).

LFT = Busy / Busy & Gate: (Jumper)

Option für die Lifetime-Messung (s.o.).

Nächste: Test-Datenquelle (TST), Vorige: Interface-Steuerung (IFS) [Inhalt]

| • Aufgabe | ||

| • Funktion | ||

| • Bedienungselemente |

Nächste: Funktion (KPL), Nach oben: Kopplungskarte (KPL) [Inhalt]

Bei manchen Experimenten (z.B. Koinzidenzexperimente) werden zu einem Ereignis mehrere Datenworte erzeugt, die nach ihrer Übertragung für die Software als zusammengehörig erkenntlich sein müssen. Diesem Zweck dient die Kopplungskarte.

Nächste: Bedienungselemente (KPL), Vorige: Aufgabe (KPL), Nach oben: Kopplungskarte (KPL) [Inhalt]

Die Kopplungskarte arbeitet wie eine normale Datenquelle, d.h. sie benötigt eine Standard-Interface-Steuerung (IFS-Karte). Der Schalter Frei/K1/K2 auf der IFS-Karte wird dabei außer Betrieb gesetzt, so dass die Kopplungskarte im Modus "Frei" läuft.

Die Kopplungskarte ist Ausgangspunkt für einen Privat-Bus, den Kopplungs-Bus, der sich nach links fortsetzt bis entweder ein Steckplatz frei ist, eine weitere Kopplungskarte auftritt, oder aber eine Karte steckt, die den Kopplungs-Bus unterbricht.

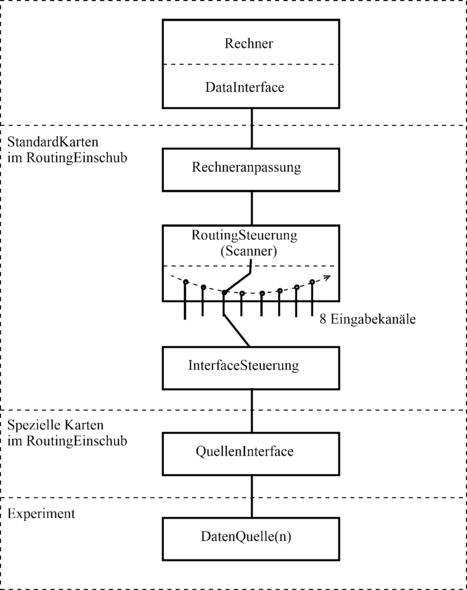

Die Kopplung wird gestartet über den BNC-Eingang Start auf der Kopplungskarte. Nach erfolgtem Start geht die Kopplung sofort in den Zustand Busy (BusyK). Das Busy steht solange an wie irgendeine der gekoppelten Quellen Busy (BusyQi) an die Kopplung meldet. Die Übertragung des Kopplungswortes trägt ihr Busy (BusyQK) wie eine normale Quelle bei. Zur Überbrückung der Reaktionszeiten der verschiedenen gekoppelten Quellen geht die Kopplung mit dem Start in eine interne Wartephase (Wait) einstellbarer Dauer. Diese Wartephase trägt ebenfalls zum Busy der Kopplung bei:

BusyK = Wait + BusyQK + Sum(i,BusyQi)

Eine eindeutige Zusammenfassung der gekoppelten Daten ist nur gewährleistet, wenn BusyK lückenlos ansteht bis alle Quellen ihre Daten registriert und abgeliefert haben. Durch geeignete Einstellung der Wartephase sollte dies immer möglich sein.

Das Signal Wait steht den gekoppelten Quellen über den Kopplungs-Bus unter dem Namen Kopplungssignal (KoppK) zu Synchronisationszwecken (Aufgaten der Quellen) zur Verfügung (Siehe Interface-Steuerung (IFS).).

Je nach eingestelltem Start-Modus unterliegt der Start der Kopplung unterschiedlichen Bedingungen:

Nach erfolgtem Start meldet die Kopplungskarte einen vorrangigen Bearbeitungswunsch bei der Routing-Steuerung an zur Übertragung eines Datenwortes, dem Kopplungswort. Durch entsprechendes Timing auf den IFS-Karten ist sichergestellt, dass das Kopplungswort auf jeden Fall vor den Datenwörtern der gekoppelten Quellen übertragen wird. Diese folgen in beliebiger Reihenfolge je nach Bearbeitungszeit in den Quellen und Stand des Routing-Scanners. Nicht alle Datenquellen müssen notwendigerweise Daten übertragen, sondern nur die, die ein Ereignis erkannt haben. Die Synchronisierung der Software erfolgt durch das Kopplungswort am Anfang eines Blockes von gekoppelten Daten.

Solange sich die Kopplung im Zustand ’Busy’ befindet, werden alle abgewiesenen Startversuche im ’Pile-up-Zähler’ registriert. Mit jeder Datenübertragung wird im Kopplungswort der Zählerstand übertragen und gleichzeitig gelöscht. Falls mehr als 255 Pile-ups auftreten, bleibt der Zähler bei 255 stehen.

Das Kopplungswort ist wie ein normales Datenwort aufgebaut. Das Kopplungs-Bit ist null. In den Daten-Bits 0-7 steht der Inhalt des Pile-up-Zählers.

Für jede am Kopplungs-Bus angeschlossene Datenquelle kann der Kopplungsmodus individuell gewählt werden über den Schalter Frei/K1/K2 auf der IFS-Karte.

Im Modus Frei nimmt die Quelle an der Kopplung nicht teil, sie läuft frei. Das von der Kopplung gelieferte Kopplungssignal (KoppK) wird nicht berücksichtigt und das Busy der Quelle wird nicht an die Kopplung gemeldet.

Im Modus K1 läuft die Quelle im wesentlichen frei. Falls jedoch der Beginn der Busy-Meldung der Quelle in das von der Kopplungskarte vorgegebene Kopplungssignal fällt, wird in der Kennung des Datenwortes das Kopplungs-Bit gesetzt. Auf diese Weise können z.B. koinzidente und nicht koinzidente Ereignisse mit dem gleichen ADC aufgenommen werden. Für Ereignisse, die das Setzen des Kopplungs-Bits zur Folge haben, wird das Busy der Quelle an die Kopplung gemeldet. Dies verhindert einen weiteren Start der Kopplung bevor die Quelle mit ihrer Bearbeitung völlig fertig ist und garantiert, dass Datenworte verschiedener Koinzidenzereignisse sauber getrennt werden. Für höhere Zählraten ist der Modus K1 nicht gut geeignet, da mit wachsender Zählrate die Wahrscheinlichkeit zunimmt, dass eine der gekoppelten Quellen noch durch ein nicht koinzidentes Ereignis busy ist. Der Start der Kopplung würde in diesem Falle zwar erfolgen, aber das Datenwort der betreffenden Quelle würde bei der Koinzidenz fehlen.

Im Modus K2 können die Quellen nur während der Dauer des Kopplungssignals Ereignisse registrieren. Das Kopplungs-Bit ist immer gesetzt, Busy wird stets an die Kopplung gemeldet. Es werden also nur koinzidente Ereignisse registriert. Ein nicht-koinzidenter Untergrund belastet das System nicht durch Totzeit.

Es ist zu beachten, dass durch die unterschiedliche Wirkungsweise des Kopplungssignals in den Modi K1 und K2 sich für das Kopplungssignal ein unterschiedliches Timing ergibt. Der Unterschied besteht darin, dass im Modus K1 das Busy der Quelle während des Kopplungssignals zum Setzen des Kopplungs-Bits führt und im Modus K2 die Quelle vom Kopplungssignal aufgegated wird, was offensichtlich dem Busy zeitlich vorausgehen muss.

Vorige: Funktion (KPL), Nach oben: Kopplungskarte (KPL) [Inhalt]

Start: (TTL-Eingang)

Durch die positive Flanke eines Signals an diesem Eingang

wird die Kopplung gestartet, falls sie nicht gerade busy

ist.

Int/Ext: (Schalter)

In Stellung Int wird die Dauer der Wartephase intern

erzeugt. Sie ist durch ein Potentiometer auf der

Frontplatte im Bereich von etwa 1-100 us einstellbar.

In Stellung Ext wird die Dauer der Wartephase durch das

Startsignal vorgegeben (high: Wartephase).

Out: (TTL-Ausgang)

Über diesen Ausgang kann das Signal Wait der Wartephase

abgenommen werden.

norm./spez.: (Steckbrücke auf der Karte)

Über diese Steckbrücke auf der Kopplungskarte kann der

Startmodus (normal bzw. spezial) eingestellt werden.

Abb. 3.4.3.1 Timing von gekoppelten Datequellen

Nächste: Bus-Signal Anzeige (BUS), Vorige: Kopplungskarte (KPL) [Inhalt]

| • Aufgabe | ||

| • Bedienungselemente |

Nächste: Bedienungselemente (TST), Nach oben: Test-Datenquelle (TST) [Inhalt]

Die Testdatenquelle erzeugt 16-Bit Datenworte zu Testzwecken. Wahlweise liefert sie mit jedem Scannerzyklus ein Datenwort ab, die Daten werden also mit der maximal möglichen Geschwindigkeit übertragen, oder die Übertragung wird durch einen externen Takt gesteuert.

Vorige: Aufgabe (TST), Nach oben: Test-Datenquelle (TST) [Inhalt]

set/count/reset: (Schalter)

ext/int: (Schalter)

prio/norm: (Schalter)

inc/alt/dec: (Schalter)

Ext-Takt: (BNC-Buchse, TTL-Eingang)

Takteingang zum externen Anstoßen einer Übertragung

(positive Flanke).

Nächste: Routing-Funktionsüberwachung (Alarm), Vorige: Test-Datenquelle (TST) [Inhalt]

Die Anzeigekarte übernimmt vom Routing-Bus die Daten- und Kontroll-Bits und zeigt sie über LED’s auf der Frontplatte an.

Anzeige:

DO ...D15 Daten-Bits

frei

frei

frei

frei

Kopp-Bit Kopplungs-Bit

LFT-Bit Lifetime-Bit

Nächste: Totzeitanzeige, Vorige: Bus-Signal Anzeige (BUS) [Inhalt]

Es werden die beiden Scanner-Takte TV und TN der Routing-Steuerung (Siehe Routing-Steuerung.) überwacht, und falls sie länger als ca. 0.5s ausbleiben, ohne dass das Routing gestoppt ist, wird Alarm gegeben. Der Alarm wird beim nächsten Scanner-Schritt wieder aufgehoben.

Anzeige (rote LED): leuchtet bei Alarm

BNC-Ausgänge für High- und Low-Signale bei Alarm

(2.5kOhm nach +5V; 330Ohm nach 0V)

Vorige: Routing-Funktionsüberwachung (Alarm) [Inhalt]

Diese Karte bildet ein zeitliches Mittel über ein digitales Totzeitsignal (TTL-Pegel) und zeigt die Totzeit auf einem Drehspulinstrument mit 100er-Skala an. Die Karte erwartet das Totzeitsignal auf der P-Bus-Leitung 28a von ihrer direkten linken Nachbarkarte. Diese muss deshalb auf 28c ein entsprechendes Signal verdrahtet haben. Für die üblichen Interface-Karten ist 28a-28c gebrückt, so dass das Signal BusyQ als Totzeitsignal zur Verfügung steht.

Nächste: Spezielle Interface-Karten, Nach oben: Top [Inhalt]

Nächste: Silena-ADC-Interface, Nach oben: Standard-Interface-Karten [Inhalt]

| • Aufgabe, Funktion | ||

| • Signalbeschreibung |

Nächste: Signalbeschreibung (D16), Nach oben: 16-Bit-Digitaleingabe [Inhalt]

Die Digitaleingabe bietet eine universelle Schnittstelle zur Eingabe von 16 Daten-Bits. Sie ist so ausgelegt, dass Laben ADC’s direkt angeschlossen werden können. Die Verbindung zur Datenquelle wird durch einen 37-poligen ERNI-Stecker hergestellt. Die Kabellänge sollte 1.5 m nicht überschreiten. Alle von der Datenquelle kommenden Leitungen sind mit 1 kOhm Pull-up-Widerständen versehen. Die Leitungen zur Datenquelle können mit max. 15 mA bei high Pegel und 24 mA bei low belastet werden.

Achtung:

Dieses Interface wurde früher auch zum Anschluss von Silena-ADCs

verwendet.

Durch einen Timer auf der alten Rechneranpassung war dafür

gesorgt, dass AcceptedB mindestens

1us lang ist. Diese Verlängerung (Silena-Änderung) war

notwendig, da der Silena-ADC eine (im Manual nicht spezifizierte)

Zeit von ca. 0.5us für ein Reset benötigt.

Diese Silena-Änderung wurde in die VME-Rechneranpassung nicht mit

übernommen, deshalb ist dieses Interface nicht mehr zum Anschluss

von Silena-ADCs geeignet. Bitte das spezielle Silena-ADC-Interface

verwenden.

Vorige: Funktion (D16), Nach oben: 16-Bit-Digitaleingabe [Inhalt]

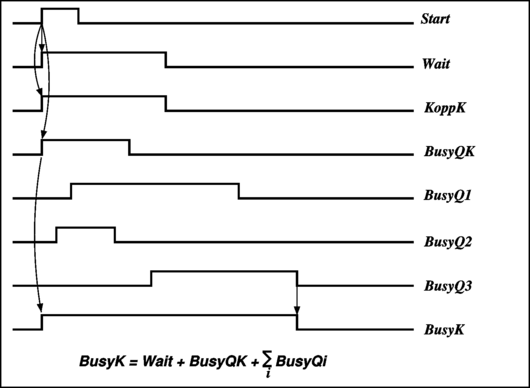

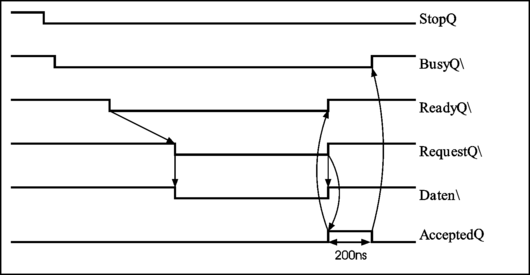

Mit Stop wird die Datenquelle gestoppt und gecleart.

Mit Ready zeigt die Datenquelle an, dass sie bereit ist ein Datenwort zu übergeben.

Mit Request wird die Datenquelle aufgefordert ihre Daten auf die Datenleitungen zu geben. Prinzipiell können die Daten immer an den Datenleitungen anstehen. Falls jedoch Pegeländerungen auf vielen Datenleitungen gleichzeitig auftreten, führt dies unweigerlich zu Störungsspitzen auf den Steuerleitungen, die zu Fehlfunktionen führen können (z.B. verfrühte Anmeldung von Ready).

Mit Accepted zeigt die Digitaleingabe an, dass die Daten übernommen wurden. Je nach Auslastung des Rechners kann das Accepted u.U. recht lange auf sich warten lassen. Normalerweise löscht die Datenquelle mit Accepted das anstehende Ready, notwendig ist dies jedoch nicht, falls beim nächsten Routing-Zyklus sofort ein weiteres Datenwort übertragen werden soll.

Mit Busy zeigt die Datenquelle an, dass sie beschäftigt ist mit der Erzeugung eines Datenwortes. Busy kann je nach Quelle mit der Vorder- oder Rückflanke von Accepted oder sonst wann verschwinden. Es wird bei einer eventuellen Totzeitmessung verarbeitet (Siehe Interface-Steuerung (IFS).).

Da je Datenleitung ein Strom von ca. 5 mA fließt, ist für eine Masseleitung von ausreichendem Querschnitt zu sorgen für die Rückführung der 16 * 5 mA = 80 mA.

Tab. 4.1.2.1 Schnittstelle zur Datenquelle

37 poliger ERNI-Stecker

Die nicht aufgeführten Anschlüsse sind unbelegt.

Signale, die mit '^' beginnen, werden von der Digitaleingabe erzeugt.

Signal ERNI-Pin

Daten-Bit 0\ 19

Daten-Bit 1\ 18

Daten-Bit 2\ 17

Daten-Bit 3\ 16

Daten-Bit 4\ 15

Daten-Bit 5\ 14

Daten-Bit 6\ 13

Daten-Bit 7\ 12

Daten-Bit 8\ 11

Daten-Bit 9\ 10

Daten-Bit 10\ 9

Daten-Bit 11\ 8

Daten-Bit 12\ 7

Daten-Bit 13\ 6

Daten-Bit 14\ 5

Daten-Bit 15\ 4

Ready\ 3

^Request 20

^Accepted 23

^Stop\ 22

Busy\ 2

^Gate 1

Masse

Abb. 4.1.2.2 Timing zwischen Digital-Eingabe und Datenquelle

Nächste: Uhr/Zaehler, Vorige: 16-Bit-Digitaleingabe, Nach oben: Standard-Interface-Karten [Inhalt]

| • Aufgabe, Funktion | ||

| • Signalbeschreibung |

Nächste: Signalbeschreibung (Silena), Nach oben: Silena-ADC-Interface [Inhalt]

Das Silena-ADC-Interface ist eine modifizierte 16-Bit-Digitaleingabe. Es berücksitigt die spezielle Steckerbelegung des Silena-ADCs, so dass die Kabelverbindung mit einem 37-poligen Flachbandkabel hergestellt werden kann. Ferner berücksichtigt es den Umstand, dass der Silena-ADC ein unterschiedlich langes (bis zu 500ns, nicht im Manual spezifiziert) Accepted-Signal benötigt.

Selbstverständlich kann diese Interface-Karte auch als universelle Schnittstelle zur Eingabe von 16 Daten-Bits verwendet werden. Die Verbindung zur Datenquelle wird durch einen 37-poligen ERNI-Stecker hergestellt. Die Kabellänge sollte 1.5 m nicht überschreiten. Alle von der Datenquelle kommenden Leitungen sind mit 1 kOhm Pull-up-Widerständen versehen. Die Leitungen zur Datenquelle können mit max. 15 mA bei high Pegel und 24 mA bei low belastet werden.

Vorige: Funktion (Silena), Nach oben: Silena-ADC-Interface [Inhalt]

Mit Stop wird der ADC gestoppt und gecleart.

Mit Ready zeigt der ADC an, dass er bereit ist ein Datenwort zu übergeben.

Request ist nicht verdrahtet, der Silena-ADC gibt deshalb seine Daten immer auf die Datenleitungen.

Mit Accepted zeigt das Interface an, dass die Daten übernommen wurden. Accepted steht so lange an bis das Ready-Signal verschwindet. Dieses Verhalten von Accepted ist notwendig, da der Silena-ADC ein im Manual nicht spezifiziertes, unterschiedlich langes (bis 500ns) Accepted benötig.

Mit Busy zeigt der ADC an, dass er beschäftigt ist mit der Erzeugung eines Datenwortes. Es wird bei einer eventuellen Totzeitmessung verarbeitet (Siehe Interface-Steuerung (IFS).).

Da je Datenleitung ein Strom von ca. 5 mA fließt, ist für eine Masseleitung von ausreichendem Querschnitt zu sorgen für die Rückführung der 16 * 5 mA = 80 mA.

Tab. 4.2.2.1 Schnittstelle zum Silena ADC

37 poliger ERNI-Stecker

Die nicht aufgeführten Anschlüsse sind unbelegt.

Signale, die mit '^' beginnen, werden vom Interface erzeugt.

Signal ERNI-Pin

Daten-Bit 0\ 1

Daten-Bit 1\ 2

Daten-Bit 2\ 3

Daten-Bit 3\ 4

Daten-Bit 4\ 5

Daten-Bit 5\ 6

Daten-Bit 6\ 7

Daten-Bit 7\ 8

Daten-Bit 8\ 9

Daten-Bit 9\ 10

Daten-Bit 10\ 11

Daten-Bit 11\ 12

Daten-Bit 12\ 13

Daten-Bit 13\ 18

Daten-Bit 14\ 37

Daten-Bit 15\ 19

Ready\ 21

^Request nicht verdrahtet

^Accepted 22

^Stop\ 20

Busy\ 15

^Gate 35

Masse 36

Abb. 4.2.2.2 Timing zwischen Interface und ADC

Nächste: Up/Down-Zaehler, Vorige: Silena-ADC-Interface, Nach oben: Standard-Interface-Karten [Inhalt]

| • Aufgabe | ||

| • Bedienungselemente | ||

| • Beispiel: Lebensdauermessung mit Totzeitkorrektur |

Nächste: Bedienungselemente (UHR), Nach oben: Uhr/Zaehler [Inhalt]

Die Uhrkarte enthält eine 16 Bit Relativzeituhr, deren Zeitregister während des Betriebes (on flight) abgefragt werden kann. Sie kann mit einem internen quarzstabilisierten Takt von 10 MHz oder extern mit bis zu 4 MHz betrieben werden. Der externe Betrieb ist gleichbedeutend mit einem Betrieb als Zähler. Beim Betrieb als Uhr besteht die Möglichkeit parallel zur eigentlichen Messungen eine zeitabhängige Totzeitmessung laufen zu lassen, um eine nachträgliche rechnerische Totzeitkorrektur zu ermöglichen. Bei Kopplung der Uhr mit anderen Datenquellen kann die gemeinsame Totzeit der gekoppelten Quellen gemessen werden.

Nächste: Beispiel (UHR), Vorige: Aufgabe (UHR), Nach oben: Uhr/Zaehler [Inhalt]

Int/Ext: (Schalter)

In Stellung Int wird die Uhr mit einem internen

quarzstabilisierten 10 MHz Takt betrieben.

In Stellung Ext kann die Uhr mit einem externen Takt bis

maximal 4 MHz betrieben werden.

Takt: (TTL-Eingang)

Über diesen Eingang kann der Uhr ein externer Takt bis zu

4 MHz zugeführt werden. Dieser wird auf den internen 10

MHz Takt aufsynchronisiert. Die positive Flanke taktet die

Uhr. Sie wird durch die Synchronisation innerhalb 100 ns

unscharf. Taktbreite und -pause müssen mindestens 125 ns

betragen.

Reset: (TTL-Eingang)

Über diesen Eingang kann die Uhr auf Null gesetzt werden.

High oder offener Eingang: Reset

min. Pulsbreite: 200 ns

Uhr: (TTL-Eingang)

Über diesen Eingang erfolgt die Abfrage der Uhr. Die

positive Flanke des Abfragesignals veranlasst die Übernahme

des Inhaltes des Uhrregisters in ein Pufferregister, wo es

bis zur Übertragung zum Rechner gespeichert wird. Die

Abfrage kann asynchron zum Takt erfolgen. Das

Abfragesignal wird auf den internen 10 MHz Takt

aufsynchronisiert. Von der Abfrage bis zur Übertragung des

Datenwortes geht die Uhrkarte in den Zustand Busy und ist

für weitere Abfragen gesperrt. Dieser Eingang ist gatebar

über die Eingänge GateQ und GateK auf der IFS-Karte.

LFT: (TTL-Eingang)

Über diesen Eingang kann zeitabhängig die ’Lifetime’ der

Uhrkarte und eventuell gekoppelter Datenquellen gemessen

werden. Er hat im wesentlichen die gleiche Wirkung wie

eine Abfrage über den Eingang Uhr mit folgenden

Unterschieden:

Die Gate-Signale wirken nicht auf diesen Eingang (änderbar). Das Datenwort hat zur Unterscheidung zusätzlich das Lifetime-Bit gesetzt. Die Abfrage ist gesperrt, wenn die IFS-Karte keine Lifetime (LFTQ) meldet.

Es wird zur Lifetime-Messung die gleiche Lifetime (LFTQ) verwendet wie auf der IFS-Karte. Diese Lifetime enthält konjunktiv die negierte Totzeit der Uhrkarte, das Signal GateQ der IFS-Karte (Option), und im Kopplungsmodus K2 die Lifetime-Meldung der Kopplung

LFTQ = BusyQ\ * GateQ(Option) * (K2\ + LFTK)

Achtung: Wird als externer Takt und zur Abfrage der Uhr (Uhr bzw. LFT) das gleiche Signal verwendet, so wird durch die Aufsynchronisierung der externen Signale auf den internen 10 MHz Takt mal der eine oder der andere Eingang früher sein. Soll ein Eingang mit Sicherheit vor dem anderen Eingang zum Zuge kommen, so müssen sie mindestens als Abstand die Taktbreite (100 ns) plus interne Laufzeitunterschiede (<50 ns) d.h. ca. 150 ns haben.

Die gleiche Zeitdifferenz ist einzuhalten zwischen einer Abfrage der Uhr und einem nachfolgenden Reset-Signal, um mit Sicherheit ein Auslesen vor dem Löschen zu erreichen.

Vorige: Bedienungselemente (UHR), Nach oben: Uhr/Zaehler [Inhalt]

Über den Eingang Uhr wird der Zeitpunkt des Auftretens der beobachteten Ereignisse zum Rechner übertragen. Die Software erzeugt daraus ein Zeitspektrum, in dem sie die Zeit als Kanaladresse interpretiert und wie im MCA-Mode im betreffenden Kanal ein ’addiere 1’ ausführt.

Über den Eingang LFT wird ein fester Takt nicht zu hoher Frequenz (damit nicht zu hohe zusätzliche Totzeit entsteht) eingegeben. Auf die gleiche Weise wie oben wird ein LFT-Spektrum erzeugt, aus dem für jeden Zeitpunkt die zugehörige Lifetime der Messung entnommen werden kann.

Nächste: 12-Bit ADC, Vorige: Uhr/Zaehler, Nach oben: Standard-Interface-Karten [Inhalt]

| • Aufgabe | ||

| • Funktion | ||

| • Eingänge (BNC-Buchsen) |

Nächste: Funktion (UDZ), Nach oben: Up/Down-Zaehler [Inhalt]

Diese Zählerkarte besitzt ein 16 Bit breites Zählerregister d.h. es kann 65535 Ereignisse registrieren. Bei Überlauf in Vorwärtsrichtung springt es auf 0 und in Rückwärtsrichtung auf 65535. Der Überlauf wird nicht angezeigt, es ist deshalb ggf. das Vorschalten eines Untersetzers zu empfehlen zur Vermeidung von Überläufen. Durch eine einfache Umverdrahtung sind jedoch auch (gekennzeichnete) Varianten entstanden, die bei Überlauf anhalten. Die Auflösungsgrenze für die Zählimpulse liegt bei ca. 200ns, d.h. 5 MHz max. Zählerfrequenz. Sollen geringere Zählimpulsabstände verarbeitet werden, bei statistisch ankommenden Signalen kann dies bereits bei geringeren Zählraten der Fall sein, so ist ein Untersetzer vorzuschalten (z.B. mit den Bausteinen 74196 (50MHz) oder 74S196 (100MHz)). Der Zählerstand kann asynchron zum Zählvorgang, d.h. ohne das Zählen zu beeinflussen, abgefragt werden. Sowohl der Zählereingang (Count) als auch der Eingang für das Auslesesignal (Read) können jeweils über Gate-Signale gesteuert werden. Alle Eingänge sind bis ca. 10V Dauerpegel gegen Überspannung geschützt und im Frequenzgang auf ca. 10 MHz begrenzt.

Nächste: Eingaenge (UDZ), Vorige: Aufgabe (UDZ), Nach oben: Up/Down-Zaehler [Inhalt]

Alle Eingangssignale werden vollständig auf verschiedene Phasen des internen 10 MHz-Taktes aufsynchronisiert, so dass der Karte die Eingangssignale völlig asynchron angeboten werden können, ohne Fehlfunktionen befürchten zu müssen. Aus diesem Aufsynchronisieren resultiert die Begrenzung der Zählfrequenz auf max. 5 MHz.

Mit dem Read-Signal wird der Inhalt des Zählregisters in ein Zwischenregister kopiert, wo er bis zur Übertragung zum Rechner gespeichert wird. Bis zum Abschluss der Übertragung befindet sich die Karte im Zustand Busy und weist weitere Read-Signale ab, d.h. der Inhalt des Zwischenregisters bleibt vom Zählvorgang unbeeinflusst. Das Zählen selber kann während des Übertragungsvorgangs völlig ungestört weitergeführt werden. Das aus dem Read-Vorgang resultierende Busy-Signal steht, bei entsprechender Verdrahtung (Siehe Interface-Steuerung (IFS).), auf der IFS-Karte an der Buchse Out zur Verfügung. Die Lifetime-Messung auf der IFS-Karte basiert ebenfalls auf dem durch den Read-Vorgang erzeugten Busy und zeigt nicht etwa die Zählverluste an. Die Totzeitverluste beim Zählen sind durch Vorschalten von Untersetzern leicht in vernachlässigbare Bereiche zu zwingen (Siehe »Totzeitbetrachtungen«.).

Vorige: Funktion (UDZ), Nach oben: Up/Down-Zaehler [Inhalt]

Count: Zähleingang

pos. flankengetriggert; ca. 5 MHz max.

Gate: Gate-Eingang für Count

High-Pegel: Gate offen

Read: Übertragen des Zählerinhaltes zum Rechner

pos. flankengetriggert;

gatebar über den GateQ-Eingang auf der IFS-Karte

Reset: Rücksetzen (auf 0) des Zählers

High-Pegel: Reset

(offener Eingang = High-Pegel!)

U/D\: Steuerung für Vorwärts/Rückwärts-Zählen

High-Pegel: Vorwärtszählen

Unbeschaltete Eingänge liegen auf High-Pegel!

Für alle Eingänge sind in Abhängigkeit von der Impulshöhe folgende minimalen Impulsbreiten erforderlich:

Pulshöhe min. Pulsbreite 5 V 25 ns 2.5 V 50 ns

Falls die Signale Read und Count bzw. Read und Reset gleichzeitig (Read bis ca. 50ns später) eintreffen, so wird zuerst die Read-Funktion ausgeführt. Soll Read nach der konkurrierenden Funktion ausgeführt werden, so muss es mindestens ca. 150ns nach dieser eintreffen. Liegt Read ca. 50 bis 150ns nach Count bzw. Reset, so ist die Reihenfolge unbestimmt.

Das Gate-Signal muss mindestens 20ns vor dem Count-Signal anstehen, damit das Zählen freigegeben wird.

Bei einer Änderung des U/D-Signals im Zeitraum von 0 bis 100ns nach dem Count-Signal ist die Zählrichtung unbestimmt.

Die angegebenen Zeitwerte sind gültig für eine Bestückung mit 74LS-Bausteinen. Sie stellen Richtwerte dar, die aufgrund von Exemplarstreuungen variieren können. In kritischen Fällen wird empfohlen, respektvollen Abstand (ca. 20ns) von den oben angegebenen Werten zu halten.

Nächste: Zaehlerbatterie, Vorige: Up/Down-Zaehler, Nach oben: Standard-Interface-Karten [Inhalt]

| • Aufgabe | ||

| • Bedienungselemente |

Nächste: Bedienungselemente (AD574), Nach oben: 12-Bit ADC [Inhalt]

Diese Routing-Karte verwendet den AD583 Sample-and-Hold-Baustein und den AD574 12-Bit-ADC-Baustein von Analog Devices zur Digitalisierung von analogen Signalen. Der ADC arbeitet nach dem Verfahren der "Sukzessiven Approximation":

Konvertierungszeit : 15us - 35us max. Abtastrate : 26kHz max. Linear.-Fehler: 1/4 LSB Der Linearitätsfehler hat sich durch Alterung inzwischen deutlich verschlechtert!

Durch zwei Schalter auf der Frontplatte (Uni/Bi, 10V/20V) können folgende Messbereiche gewählt werden:

10V 20V Uni: 0V - +10V 0V - +20V Bi : -5V - +5V -10V - +10V

Vorige: Aufgabe (AD574), Nach oben: 12-Bit ADC [Inhalt]

P1: (Poti)

Offset-Abgleich für Bipolar-Modus des AD574 ADC-Bausteins

P2: (Poti)

Full-Scale-Abgleich für Bipolar-Modus des AD574 ADC-Bausteins

P3: (Poti)

Offset-Abgleich für Unipolar-Modus des AD574 ADC-Bausteins

P4: (Poti)

Offset-Abgleich des AD583 Sample-and-Hold-Bausteins

Uni/Bi: (Schalter)

Einstellung von uni- oder bipolarem Modus

10V/20V: (Schalter)

Messbereichseinstellung 10V oder 20V

Analog: (Analog-Eingang)

Eingang für das zu messende Analog-Signal

Gate: (TTL-Eingang)

Gate-Eingang für das Sample-Signal

High-Pegel: Gate offen

(offener Eingang = High-Pegel)

Sample: (TTL-Eingang)

Eingang für das Trigger-Signal.

Eine positive Flanke startet eine Konvertierung.

Nächste: Breiten- und Abstandsverteilung, Vorige: 12-Bit ADC, Nach oben: Standard-Interface-Karten [Inhalt]

| • Aufgabe | ||

| • Funktion | ||

| • Zählerkarten |

Nächste: Funktion (ZLR), Nach oben: Zaehlerbatterie [Inhalt]

Die Zählerbatterie benötigt wie jede andere Datenquelle eine IFS-Karte (Siehe Interface-Steuerung (IFS).) direkt links neben der Zählersteuerung (ZLRS). Rechts anschließend sind die Zählerkarten (ZLRx) zu stecken bis zu einer maximalen Anzahl von 255 einzelnen Zählern. Jeder Zähler kann im allgemeinen nur ein Ereignis speichern und verwirft dann alle folgenden Ereignisse bis das gespeicherte Ereignis zum Rechner übertragen wurde. Die Zählersteuerung fragt reihum alle Zähler ab und sobald sie auf ein gespeichertes Ereignis stößt, überträgt sie die Nummer des Zählers zum Rechner und löscht den Speicher. Mit der Standard-Software zur Aufnahme von Spektren wird jedem Zähler ein Kanal im Spektrum zugeordnet. Die Nummerierung der Zähler beginnt bei der ersten Karte rechts von der Zählersteuerung und setzt sich auf den jeweils folgenden Zählerkarten fort. Im allgemeinen sind acht Zähler auf einer Karte untergebracht, wobei jedoch möglicherweise nicht alle von extern zugänglich sind (z.B. nur 4), weil die restlichen die Totzeitverluste ihrer Nachbarn registrieren.

Die Abfrage der Zähler erfolgt mit 5MHz. Ein voller Zyklus, in dem alle Zähler einmal abgefragt werden, dauert daher N * 200ns, falls keine Daten übertragen werden, wobei N die Anzahl der angeschlossenen Zähler ist. Werden Daten übertragen, so verlängert sich die Zeit. Die maximale Rate aller Zähler zusammen ist begrenzt durch die Übertragungskapazität der Verbindung zum Rechner.

Bei zu hohen Zählraten ist zur Vermeidung von Totzeitverlusten die Vorschaltung eines Untersetzers zu empfehlen (z.B. 1/10) (Siehe »Vorgeschaltete Untersetzer«.).

Nächste: Zaehlerkarten (ZLR), Vorige: Aufgabe (ZLR), Nach oben: Zaehlerbatterie [Inhalt]

Die Zählerbatterie besteht aus einer Zählersteuerung (ZLRS) und mehreren Zählerkarten (ZLRx) mit jeweils mehreren Zählern. Die Zählersteuerung fragt reihum alle Zähler mittels eines Abfrage-Bits (Select-Bit) ab (5MHz). Jede Zählerkarte enthält ein Schieberegister mit seriellem Eingang und parallelen Ausgängen, je einer für jeden Zähler, durch das dieses Abfrage-Bit geschoben wird. Ein Zähler ist selektiert, wenn das Bit auf dem ihm zugeordneten Ausgang erscheint. Falls er dann ein Ereignis gespeichert hat, meldet er über den PrivatBus ein ’Ready’ zur Zählersteuerung. Diese überträgt daraufhin (ReadyQ) die in einem 8-Bit-Register mitgezählte Nummer des selektierten Zählers an den Rechner. Mit der Quittung auf die Übertragung (AcceptedQ) wird der selektierte Zähler gelöscht und die Abfrage fortgesetzt.

Der Abfragezyklus passt sich der Anzahl der vorhandenen Zähler an. Zu diesem Zweck übergibt jede Zählerkarte eine Anfangs- (AM) und Endemeldung (EM) an die Zählersteuerung. Erscheint mit dem folgenden Takt nach einer EM keine AM, so bedeutet dies für die Zählersteuerung, dass die nächstfolgende Karte fehlt. Sie setzt daraufhin den Nummernzähler (8-Bit-Register) auf Null, löscht die Schieberegister aller Zählerkarten und generiert ein neues ’Select-Bit’.

Falls der Nummernzähler überläuft aufgrund eines Funktionsfehlers, oder weil mehr als 255 Zähler angeschlossen sind, so wird dies über eine LED auf der Frontplatte angezeigt. Ferner wird der Abfragezyklus abgebrochen und bei Zähler Null wieder begonnen. Die Fehleranzeige ist nur durch einen ’Stop’ zu löschen.

Die Zählersteuerung meldet Busy (BusyQ) solange das einsynchronisierte Ready eines Zählers oder die Quittung des Routing (AcceptedQ) ansteht. Solange BusyQ ansteht ist der Schiebetakt gesperrt.

Ein manueller oder Rechner-Stop (StopQ) erzeugt ein Reset-Signal (Reset), das die Synchronisier-FF’s für die Ready-Meldung und den gerade angewählten Zähler zurücksetzt. Da der Schiebetakt weiterläuft, werden bei anstehendem StopQ reihum alle Zähler immer wieder gelöscht, ohne dass dabei Daten übertragen werden.

Vorige: Funktion (ZLR), Nach oben: Zaehlerbatterie [Inhalt]

| • ZLR1 - Vierfachzähler mit Überlaufregistrierung (TTL-Eingänge) |

Nach oben: Zaehlerkarten (ZLR) [Inhalt]

Die Karte enthält 8 Zähler, wobei jedoch nur die Zähler 0,2,4,6 extern zugänglich sind. Die Zähler 1,3,5,7 dienen dazu, die Totzeitverluste jeweils ihrer Vorgänger zu registrieren. Auf diese Weise können Totzeitkorrekturen durchgeführt werden.

Über einen ’Gate’-Eingang können die Zähler an- und abgestellt werden. Das Gate-Signal beeinflusst nicht bereits gespeicherte Ereignisse. Der Gate-Eingang ist konjunktiv (UND) verknüpft mit dem Gate-Signal von der IFS-Karte, d.h. beide Signale müssen auf High-Potential liegen, wenn die Zähler arbeiten sollen. Offene Anschlüsse liegen auf high.

Über eine LED wird angezeigt, wenn einer der Zähler ein Ereignis an das Routing überträgt.

Bedienungselemente, Anzeigen

0, 2, 4, 6: (BNC-Buchsen, TTL-Eingänge)

Eingänge für die vier Zähler 0,2,4,6. Gezählt werden die

Low-High-Übergänge. Falls der geradzahlige Zähler bereits ein

Ereignis speichert, wird der nächstfolgende ungeradzahlige

Zähler gesetzt. Ist auch dieser belegt, so geht das Ereignis

verloren.

Anzeige: (LED)

Die LED leuchtet immer, wenn einer der 8 Zähler ein Ereignis

an den Rechner überträgt.

Nächste: Abstandsverteilung, Vorige: Zaehlerbatterie, Nach oben: Standard-Interface-Karten [Inhalt]

| • Aufgabe, Funktion | ||

| • Bedienungselemente |

Nächste: Bedienungselemente (BAV), Nach oben: Breiten- und Abstandsverteilung [Inhalt]

Die BAV-Karte misst mit Hilfe der Uhr-/Zähler-Karte (s.h 4.2) die Breite eines TTL-Signals oder den Abstand von zwei aufeinander folgenden TTL-Signalen. Die zeitliche Auflösung der Messung ist die der Uhr-Karte, bei internem Takt also 100ns. Die maximal messbaren Breiten bzw. Abstände sind durch ein Poti auf der Frontplatte im Bereich von ca. 50us bis 2ms einstellbar. Nach Ablauf des Zeitlimits wird die Karte zurückgesetzt und kann nach ca. 100ns das nächste Signal verarbeiten, um eine neue Messung zu beginnen. Werden die von der Uhr-Karte übertragenen Messdaten mit einem Vielkanal-Programm (z.B. MCA) erfasst, so erhält man als ’Spektrum’ die zeitliche Verteilung von Breite oder Abstand.

Die BAV-Karte muss direkt rechts neben der Uhr-Karte stecken und erhält von dieser über die P-Bus-Leitung 28a das BusyQ-Signal. Solange die Uhr-Karte busy meldet, werden von der BAV-Karte keine Eingangssignale verarbeitet.

Breitenverteilung

Es wird der zeitliche Abstand zwischen ansteigender und

abfallender Flanke des Eingangssignals gemessen. Bei nicht zu

hoher Signalrate kann jedes Signal gemessen werden.

Abstandsverteilung

Es wird der zeitliche Abstand zwischen den ansteigenden

Flanken zweier aufeinander folgender Eingangssignale gemessen.

Daher kann bestenfalls nur jeder zweite Abstand gemessen

werden.

Vorige: Aufgabe (BAV), Nach oben: Breiten- und Abstandsverteilung [Inhalt]

Breite/Abstand: (Schalter)

Umschaltung von Breite- auf Abstands-Messung

Limit: (10-Gang-Poti)

Einstellung des Zeitlimits (50us - 2ms) für die einzelne

Messung

Reset: (BNC-Ausgang)

Ansteuerung des Reset-Eingangs der Uhr-Karte

Uhr: (BNC-Ausgang)

Ansteuerung des Uhr-Eingangs der Uhr-Karte

Puls: (BNC-Eingang)

Eingang für das zu messende TTL-Signal

Vorige: Breiten- und Abstandsverteilung, Nach oben: Standard-Interface-Karten [Inhalt]

| • Aufgabe | ||

| • Funktion | ||

| • Bedienungselemente | ||

| • Beispiele für Abstandsverteilungen | ||

| • Tabellen |

Nächste: Funktion (SAV), Nach oben: Abstandsverteilung [Inhalt]

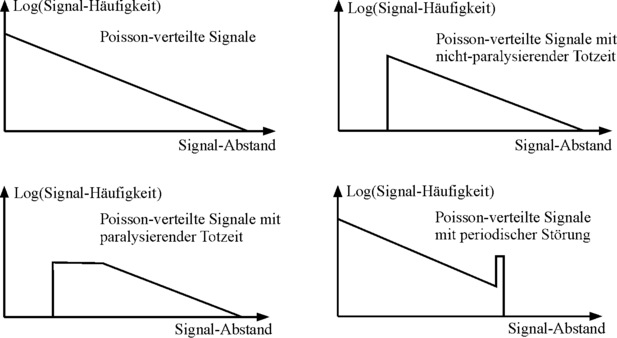

Bei vielen Experimenten (z.B. Wirkungsquerschnittsmessungen) ist es wichtig zu wissen in wie weit die erwartete Poisson-Verteilung der Ereignisse gestört ist z.B. durch Totzeit, Nachimpulse des Detektors, periodische Störungen usw.. Als eine geeignete Diagnosemöglichkeit bietet sich das Messen der Abstandsverteilung der Ereignisse an. Für Poisson-verteilte Ereignisse sind die Abstände exponentiell abfallend verteilt, in logarithmischer Darstellung erhält man also eine Gerade. Damit können Abweichungen von der Poisson-Verteilung rasch erkannt werden. Selbst mit dem Auge nicht mehr sichtbare Abweichungen können leicht durch einen Fit mit statistischer Wichtung aufgespürt werden, wenn das reduzierte Chi-Quadrat nicht in der Nähe von 1 liegt (Chi-Quadrat-Test, sh. Tab.).

Die Abstände zeitlich statistischer Signale (Poisson-Verteilung) sind exponentiell abfallend verteilt, d.h. in Log-Darstellung als abfallende Gerade.

Durchlaufen solche Signale eine nicht-paralysierende Totzeit, d.h. Signale, die in eine Totzeit fallen verlängern diese nicht, so erhält man wiederum die gleiche exponentielle Verteilung, aber um die Totzeit verschoben und um die Totzeitverluste vermindert.

Für eine paralysierende Totzeit, bei der jedes Signal, das in die Totzeit seines Vorgängers fällt, nur die Totzeit verlängert aber selbst nicht durchkommt, ist das der Totzeit nachfolgende mehr oder weniger ebene Dach charakteristisch. Mit zunehmender Zählrate wird der Abfall zunächst steiler und dann wieder flacher bis schließlich kein Ereignis mehr passieren kann.

Bei einer periodischen Störung in Poisson-verteilten Signalen können nur maximale Abstände in der Länge der Periode der Störung auftreten.

Mehr zu Totzeitverlusten und Abstandsverteilungen finden Sie unter Zählratenstatistik.

Nächste: Bedienungselemente (SAV), Vorige: Aufgabe (SAV), Nach oben: Abstandsverteilung [Inhalt]

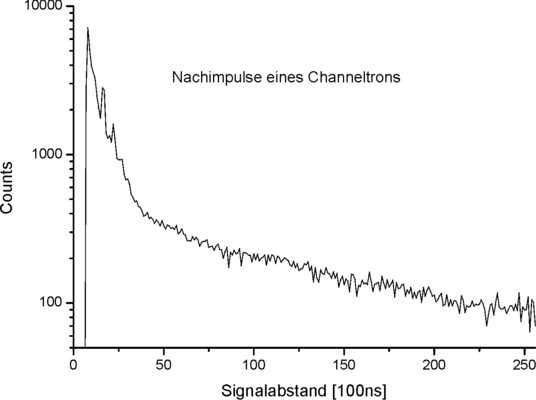

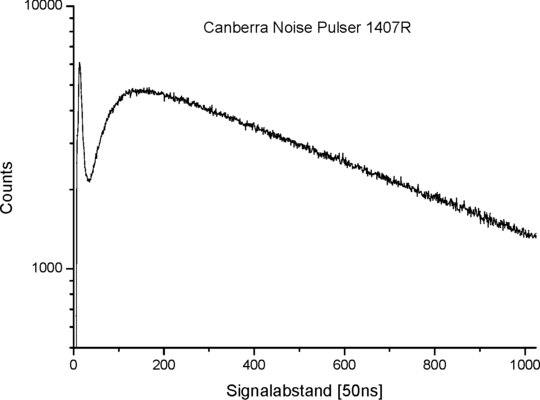

Es wird der zeitliche Abstand zwischen den ansteigenden Flanken zweier aufeinander folgender Eingangssignale gemessen. Für zufällige Ereignisse könnte man die Messung zu irgendeinem beliebigen Zeitpunkt starten und würde immer die richtige Abstandsverteilung erhalten, da die Vorgeschichte nicht in die Messung eingeht. Da jedoch auch nicht zufällige Signale wie Nachimpulse von Detektoren, periodische Störungen usw. richtig vermessen werden sollen, wird der exakte Abstand zwischen zwei aufeinanderfolgenden Signalen gemessen, was einen deutlich höheren Hardware-Aufwand bedeutet, da jedes Signal gleichzeitig Stop und Start einer Messung ist.

Die Zeitmessung erfolgt mit einer 20Mhz Quarzuhr, d.h. mit einer Auflösung von 50ns. Niedrigere Zeittakte sind durch Austausch des Quarzoszillators möglich. Für höhere Frequenzen muss jedoch ein schnellerer ispLSI-Baustein (1032E-100MHz) eingesetzt werden.

Die Zeitmessung erfolgt mit 16 Bits, bei einer Taktfrequenz von 20MHz können also Pulsabstände bis 3.27675ms gemessen werden. Darüber hinaus gehende Abstände werden im letzten Kanal (65535) gesammelt. Der Kanal 0 entspricht dem Abstand 0, der aus verständlichen Gründen nicht gemessen werden kann. Der Übergang von einem Kanal zum nächsten erfolgt linear gleitend, d.h. Abstände der Länge n+p (n ganz, p<1) tragen 1-p Anteile zum Kanal n und p Anteile zum Kanal n+1 bei.

!!! Bei Verwendung des Messprogrammes MCA mit dem Display-Programm Peak ist zu beachten, dass die Kanäle von 1 ab gezählt werden!!!

Totzeitverluste

Damit nach einer erfolgten Abstandsmessung nicht erst auf die Übertragung

der Daten gewartet werden muss und dadurch das nächste Intervall

verloren geht, ist dem Uhrregister ein 2-stufiger Fifo-Speicher

nachgeschaltet. Gemäß der Poisson-Verteilung der eintreffenden

Signale können jedoch zufälligerweise mehrere kurze Intervalle

hintereinander eintreffen, so dass die Kanalkapazität des Übertragungsweges

überschritten wird und Daten verloren gehen. Bei statistischen Pulsen

verzerren diese Verluste nicht die Abstandsverteilung bei periodischen

Pulsen können allerdings Interferenzen auftreten (s.u.)

Da der Fifo-Speicher die statistischen Schwankungen ausgleicht, minimiert er deutlich die Totzeitverluste (sh. Tab.)

Interferenzen bei periodischer Pulsfolge

Bei gewissen periodischen Mustern von kurzen und langen Abständen

können Interferenzen mit der internen Ablaufsteuerung auftreten,

die die gemessene Abstandsverteilung verzerren. Bei einer Fifo-Tiefe

von 2 würde z.B. eine periodische kurz-kurz-lang Abstandsfolge

dazu führen, dass jeder zweite lange Abstand durch Totzeit

verloren geht. Kurz bedeutet kürzer als die halbe

Datenübertragungszeit und lang bedeutet länger als die

dreifache Datenübertragungszeit. Eine kurz-lang Abstandsfolge

würde hingegen richtig wiedergegeben.

Nächste: Beispiele (SAV), Vorige: Funktion (SAV), Nach oben: Abstandsverteilung [Inhalt]

Puls: (BNC-Eingang)

Eingang für das zu messende TTL-Signal > 20ns

Nächste: Tabellen (SAV), Vorige: Bedienungselemente (SAV), Nach oben: Abstandsverteilung [Inhalt]

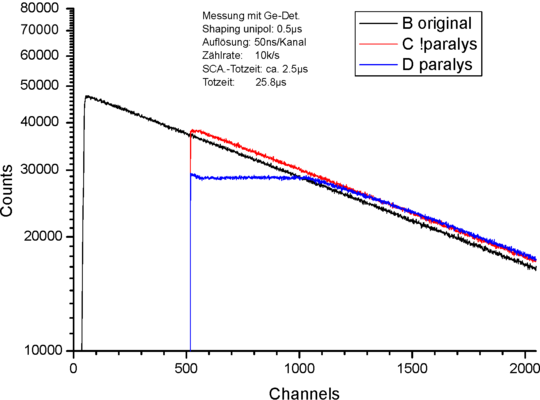

Totzeit (500ns) und Nachimpulse (bis ca. 4 us) eines Channeltrons.

Der "Noise Pulsers" 1407R von Canberra zeigt eine markante Abweichung von der Poisson-Statistik unterhalb von 10 us.

Ge-Detektorsignale bei Verwendung eines Hauptverstärkers (, 500ns Shaping, unipolar) mit "Pole-Zero-Cancellation".

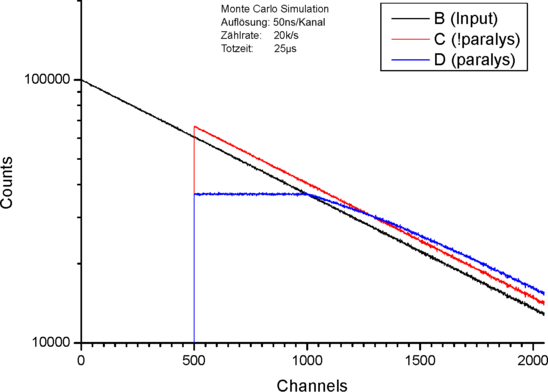

Monte-Carlo-Simulation der Abstandsverteilung nach einer Totzeit bei Poisson-verteilter Eingangsrate.

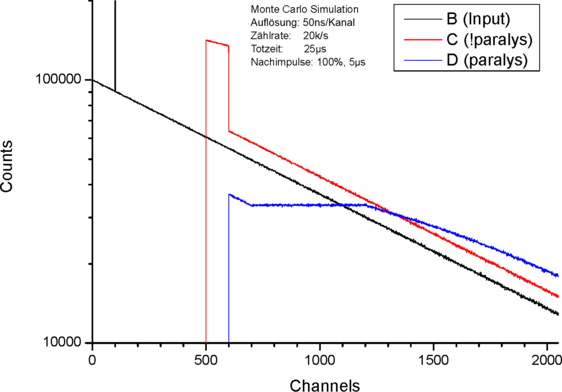

Monte-Carlo-Simulation der Abstandsverteilung nach einer Totzeit bei Poisson-verteilter Eingangsrate mit 100% Nachimpulsen.

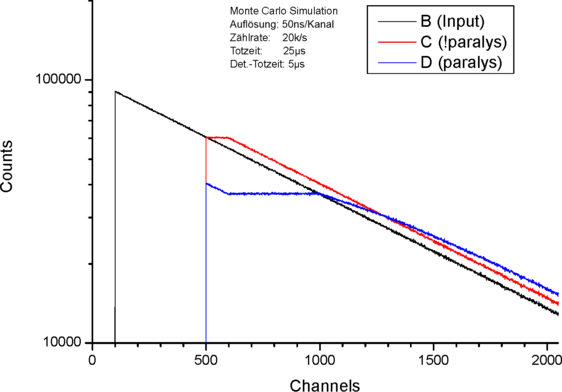

Monte-Carlo-Simulation der Abstandsverteilung nach einer Totzeit bei Poisson-verteilter Eingangsrate, die bereits eine vorausgegangene nicht paralysierende Totzeit durchlaufen hat.

Vorige: Beispiele (SAV), Nach oben: Abstandsverteilung [Inhalt]

Chi-Quadrat Test (1-P)

(1-P): Wahrscheinlihkeit, dass redChi^2 kleiner ist

Freiheitsgrade

redChi^2 200 400 600 800 1000 1200

0.900 0.1582 0.0749 0.0380 0.0200 0.0107 0.0058

0.920 0.2151 0.1273 0.0800 0.0518 0.0341 0.0227

0.940 0.2813 0.1998 0.1488 0.1135 0.0878 0.0686

0.960 0.3549 0.2912 0.2473 0.2135 0.1863 0.1637

0.980 0.4333 0.3970 0.3709 0.3497 0.3317 0.3158

1.000 0.5133 0.5094 0.5077 0.5066 0.5059 0.5054

1.020 0.5917 0.6196 0.6418 0.6606 0.6769 0.6916

1.040 0.6657 0.7197 0.7590 0.7899 0.8153 0.8366

1.060 0.7329 0.8039 0.8504 0.8836 0.9083 0.9271

1.080 0.7918 0.8699 0.9146 0.9425 0.9606 0.9728

1.100 0.8417 0.9182 0.9551 0.9746 0.9854 0.9915

Totzeitverluste bei statistischen Pulsen Verluste: 1 - exp(-RT) * (1 + RT + RT**2/2 +..+ RT**n/n!) R: Datenrate T: Totzeit = 3000ns mittel, 5200ns max, nicht paralysierend n+1: Fifo-Tiefe Bei RT > 1 wird die Kanalkapazitaet ueberschritten und es kommt zum Datenstau. RT \ 1 2 3 4 Fifo-Tiefe 0.00 0.0000 0.0000 0.0000 0.0000 0.02 0.0198 0.0002 0.0000 0.0000 0.04 0.0392 0.0008 0.0000 0.0000 0.06 0.0582 0.0017 0.0000 0.0000 0.08 0.0769 0.0030 0.0001 0.0000 0.10 0.0952 0.0047 0.0002 0.0000 0.15 0.1393 0.0102 0.0005 0.0000 0.20 0.1813 0.0175 0.0011 0.0001 0.25 0.2212 0.0265 0.0022 0.0001 0.30 0.2592 0.0369 0.0036 0.0003 0.35 0.2953 0.0487 0.0055 0.0005 0.40 0.3297 0.0616 0.0079 0.0008 0.45 0.3624 0.0754 0.0109 0.0012 0.50 0.3935 0.0902 0.0144 0.0018 0.60 0.4512 0.1219 0.0231 0.0034 0.70 0.5034 0.1558 0.0341 0.0058 0.80 0.5507 0.1912 0.0474 0.0091 0.90 0.5934 0.2275 0.0629 0.0135 1.00 0.6321 0.2642 0.0803 0.0190

Nächste: Zaehlratenstatistik, Vorige: Standard-Interface-Karten, Nach oben: Top [Inhalt]

Diese Interface-Entwicklungen werden hier nur aufgelistet und sind in den Unterlagen für die einzelnen Experimente im Detail beschrieben. Diese Aufstellung enthält auch Oldies, in der Hoffnung, sie eines Tages wieder recyclen zu können.

| • Elektron-Positron-Spaltfragment-Winkelverteilungs-Experiment (K5) | ||

| • Ion-Ion-Stoß-Experiment (Labor 016) | ||

| • Elektron-Ion-Stoß-Experiment (Labors 017, SI) |

Nächste: Ion-Ion-Stoss, Nach oben: Spezielle Interface-Karten [Inhalt]

EPOS-Steuerung

EPOS-Messprogramm

Eingabe des LB-Triggers und Generierung von Gate- und

Delay-Signalen für die "in beam" und "out of beam" Messphasen.

Nächste: Elektron-Ion-Stoss, Vorige: EPOS-Steuerung, Nach oben: Spezielle Interface-Karten [Inhalt]

LIC-Interface

IIM-, IIC-, LIC-Messprogramme

Umschalter IIM-, IIC-, LIC-Messungen; Kontrolle der

LIC-Positions-Laufzeit-Messung

TAKT-Karte

IIC-, IIF-, IIP-, LIC-, LIP-Messprogramme

Takte zum Auslesen der Zählerkarten; Totzeitmessung

IIM-Interface

IIM-, LIC-Messprogramme

Interface zum SSL-2401 Position-Computer

LII-Interface

LII-, LIP-Messprogramme

FIFO-gepufferte Dateneingabe für

Pulsed-Beam-Koinzidenz-Experimente; Interface zum SSL-2401

Position-Computer

Vorige: Ion-Ion-Stoss, Nach oben: Spezielle Interface-Karten [Inhalt]

ESS-Kontrolle

ESS-Messprogramm

Totzeit-Überwachung.

ESS-Kanalnummer-Eingabe

ESS-Messprogramm

Interface für parallele Eingabe der aktuellen Kanalnummer.

DRM-Interface

DRM-Messprogramm

Interface zum SSL-2401 Position-Computer

Nächste: Technische Details, Vorige: Spezielle Interface-Karten, Nach oben: Top [Inhalt]

Die Zählratenstatistik ist inzwischen zu einem eigenen Paper geworden.

HTML-Version:

http://www.strz.uni-giessen.de/ExpHelp/statistik/statistik.html

PDF-Version:

http://www.strz.uni-giessen.de/ExpHelp/statistik/statistik.pdf

Nächste: Oldies, Vorige: Zaehlratenstatistik, Nach oben: Top [Inhalt]

| • Routing-Bus | ||

| • Komponenten und Schnittstellen | ||

| • Schaltungsunterlagen |

Nächste: Komponenten und Schnittstellen, Nach oben: Technische Details [Inhalt]

| • Routing-Bus Signale | ||

| • Routing-Bus Abschluss |

Nächste: Routing-Bus Abschluss, Nach oben: Routing-Bus [Inhalt]

Der Routing-Bus (Tab. 7.1.1.1) besteht aus zwei Teilen, dem ’Allgemeinen Bus’, der über die ganze Breite des Überrahmens geht und dem ’Privat-Bus’, der erst durch das Stecken benachbarter Karten entsteht und auf diese begrenzt ist.

Allgemeiner Bus (A-Bus)

Der allgemeine Bus belegt die Anschlüsse 1a, 1c usw. bis 21c.

Die Anschlüsse mit dem Suffix a und c führen

im Gegensatz zum Privat-Bus zu verschiedenen Bus-Leitungen und

dürfen nicht gebrückt werden.

+ 5V / 10A +15V / 1A -15V / 1A

TN: Normal-Scanner TV: Vorrang-Scanner

Privat-Bus (P-Bus)

Der Privat-Bus baut sich erst durch Stecken der Karten auf.

Eine fehlende Karte oder das Fehlen entsprechender Brücken auf

den Karten unterbrechen den Privat-Bus. Er reicht von den

Leitungen 22 bis 32 einschließlich. Die Leitungen mit dem

Suffix a führen zur linken Nachbarkarte und die mit c zur

rechten. Soll ein Bus aufgebaut werden, so sind die Anschlüsse

a und c einer Leitung zu brücken. Die individuelle Nutzung des

Privat-Busses ist den einzelnen Kartenbeschreibungen zu

entnehmen (z.B. RST-, IFS-, KPL- Karten).

Tab. 7.1.1.1 Data-Routing-Bus

a Pin c

----------------------------------------------------------

Spannungs- (digital) +5V 1 +5V (digital) Spannungs-

Versorgung (digital) 0V 2 0V (digital) Versorgung

----------------------------------------------------------

D0\ 3 D1\

D2\ 4 D3\

D4\ 5 D5\

D6\ 6 D7\

D8\ 7 D9\

D10\ 8 D11\

D12\ 9 D13\

D14\ 10 D15\

A-Bus Kopp-Bit\ 11 LFT-Bit\ A-Bus

SAddr0\ 12 1MHz-Clock

SAddr1\ 13 PAddr1\

SAddr2\ 14 PAddr2\

SAddr3\ 15 PAddr3\

RequestB 16 ReadyB\

StopB\ 17 AcceptedB

10MHz-Clock\ 18 10MHz-Clock

TV 19 TN

(analog) 0V 20 PrioReqB\

(analog) +15V 21 -15V (analog)

----------------------------------------------------------

22

23

24

25

P-Bus 26 P-Bus

27

28

29

30

31

32

----------------------------------------------------------

(Signalnamen mit '\': aktiv low)

Vorige: Routing-Bus Signale, Nach oben: Routing-Bus [Inhalt]

Der Bus-Abschluss ist normalerweise ganz links auf der

Rückseite der ersten VG-Steckerleiste installiert. Es bestehen

jedoch auch Sonderlösungen durch von vorne gesteckte Karten,

insbesondere wenn der Überrahmen in einen Data-Routing-Bus und

einen Control-Routing-Bus aufgeteilt ist.

Der Bus-Abschluss ist je nach Aufgabe der Bus-Leitungen als

aktiver Abschluss (ca. 3V) oder durch Pulldown-Widerstände

realisiert (Abb. 7.1.2.1). Der 27 Ohm Widerstand, mit denen

die Pulldowns zusammengefasst sind, ist experimentell ermittelt

und verbessert die Signale ganz erheblich. Insbesondere

vermindert er ein Übersprechen, das im Data-Routing zum

Ausfall einzelner 10MHz-Takte beim Schalten der

SADR(0:3)-Leitungen geführt hatte. Warum das Ganze gerade in

dieser Beschaltung ordentlich läuft, weiß keiner so recht. Die

von den Interface-Karten erzeugten Signale können mittels

Treiber-Bausteinen mit mindestens 15mA (besser 24mA)

Low-Signalstrom (z.B. ’LS245, ’LS373, ’LS374) auf den Bus

gegeben werden.

Bei der Entwicklung von Interface-Karten bitte stets darauf

achten, dass sowohl Sender- als auch Empfänger-Bausteine

möglichst nahe am Bus platziert werden! Denn ein solcher Bus

ist eine sehr heikle Hf-Übertragungsstrecke (ca. 20MHz), die

man durch falsch aufgebaute Steckkarten empfindlich stören

kann.

Abb. 7.1.2.1 Routing-Bus-Abschluss

D00\ 3a <--220Ohm--|

D01\ 3c <--220Ohm--|

D02\ 4a <--220Ohm--|

D03\ 4c <--220Ohm--|

D04\ 5a <--220Ohm--|

D05\ 5c <--220Ohm--|

D06\ 6a <--220Ohm--|

D07\ 6c <--220Ohm--| +---------+

D08\ 7a <--220Ohm--| | aktiver |

D09\ 7c <--220Ohm--+---------|Abschluss|

D10\ 8a <--220Ohm--| | 3 Volt |

D11\ 8c <--220Ohm--| +----+----+

D12\ 9a <--220Ohm--| |

D13\ 9c <--220Ohm--| ===

D14\ 10a <--220Ohm--|

D15\ 10c <--220Ohm--|

Kopp-Bit\ 11a <--220Ohm--|

LFT-Bit\ 11c <--220Ohm--|

1MHz-Clock 12c <--220Ohm--|

ReadyB\ 16c <--220Ohm--|

PrioReqB\ 20c <--220Ohm--|

PADR1\ 13c )

PADR2\ 14c ) Steckplatzkodierung 0V/5V

PADR3\ 15c )

SADR0\ 12a <--220Ohm--|

SADR1\ 13a <--220Ohm--| +---------+

SADR2\ 14a <--220Ohm--| |passiver |

SADR3\ 15a <--220Ohm--+---------|Abschluss|

RequestB\ 16a <--220Ohm--| | 27 Ohm |

StopB\ 17a <--220Ohm--| +----+----+

AcceptedB 17c <--220Ohm--| |

10MHz-Clock\ 18a <--220Ohm--| ===

10MHz-Clock 18c <--220Ohm--|

TV 19a <--220Ohm--|

TN 19c <--220Ohm--|

(analog) 0V 20a <--220Ohm--|

Nächste: Schaltungsunterlagen, Vorige: Routing-Bus, Nach oben: Technische Details [Inhalt]

Abb. 7.2.0.1 Komponenten und Schnittstellen des Routing

Nächste: Quellen-Interface <-> Interface-Steuerung, Nach oben: Komponenten und Schnittstellen [Inhalt]

Eine solche Schnittstelle existiert immer dann, wenn ein bereits vorhandenes Gerät angeschlossen werden soll (z.B. ein Silena ADC wird mittels Silena-ADC-Interface an das Routing angepasst) und ist i.a. ausschließlich für diesen Zweck ausgelegt.

Nächste: Interface-Steuerung, Vorige: Datenquellen <-> Quellen-Interfaces, Nach oben: Komponenten und Schnittstellen [Inhalt]

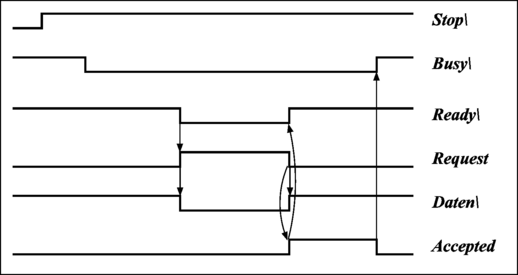

Die IFS-Karte baut nach rechts einen Privat-Bus den IFS-Bus zum Quellen-Interface hin auf. Er endet normalerweise beim Quellen-Interface, wobei dieses jedoch aus mehreren Karten bestehen darf. Alle Signalnamen auf dem IFS-Bus enden mit Q. Die Signalbezeichnungen sind in positiver Logik angegeben, d.h. wenn an einer Leitung ’high’ anliegt, so ist das zugehörige Signal wahr. Ein Backslash "\" bedeutet die Negierung eines Signals: BUSY\ = NOT (BUSY). Wenn also eine Datenquelle Busy meldet, dann liegt ’low’ auf der Leitung BUSY\. Mit ’^’ gekennzeichnete Signale werden auf der IFS-Karte erzeugt.

^LFTQ\: (Lifetime Quelle)

Dieses Signal wird auf der IFS-Karte erzeugt und stellt

die Lifetime (=NOT(Totzeit)) zur Verfügung. LFTQ setzt

sich konjunktiv (UND) zusammen aus der negierten

Busy-Meldung der Datenquelle (BusyQ\), dem Eingang GateQ

der IFS-Karte (Option), und im Kopplungsmodus K2 der

Lifetime-Meldung LFTK der Kopplung.

LFTQ= BusyQ\ * GateQ(Option) * (K2 * LFTK\)\

PrioReqQ\: (Vorrang Quelle)

Dieses Signal zeigt der IFS-Karte an, dass die Quelle mit

Vorrang bedient zu werden wünscht. Es kann statisch

anstehen, mit ReadyQ wird es wirksam. PrioReqQ schaltet die

IFS-Karte in den Kopplungsmodus Frei. Eine Datenquelle,

die mit Vorrang läuft, kann deshalb nicht an einer

Datenkopplung teilnehmen.

^GateSQ: (Gate Quelle)

Mit diesem Signal gatet die IFS-Karte die angeschlossene

Datenquelle auf- und zu.

BusyQ: (Busy Quelle)

Mit diesem Signal meldet die Datenquelle ihr Busy an die

IFS-Karte.

^StopQ: (Stop Quelle)

Dieses Signal teilt der Datenquelle mit, dass ihr keine

Daten vom Routing abgenommen werden. Als Ursachen hierfür

kommen in Frage:

Normalerweise cleart dieses Signal die Datenquelle.

ReadyQ\: (Data Ready Quelle)

^RequestQ: (Data Request Quelle)

^AcceptedQ: (Data Accepted Quelle)

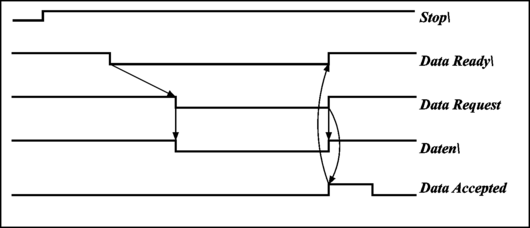

Diese drei Signale bilden zusammen einen Hand-Shake-Dialog

(Abb. 7.2.2.2) zur Übernahme der Daten von der Quelle.

Mit ReadyQ teilt die Datenquelle der IFS-Karte mit, dass

sie ein Datenwort übertragen möchte. Dieses Signal muss

zumindest bis zum Beginn von RequestQ anstehen.

Mit RequestQ fordert die IFS-Karte die Datenquelle auf,

für die Dauer des Signals ihre Daten auf den Bus zu geben.

Mit AcceptedQ wird der Datenquelle mitgeteilt, dass die

Daten übernommen wurden.

Daten(0-15): (Datenleitungen)

Die Daten laufen nicht über die IFS-Karte sondern werden

direkt auf den Routing-Bus gegeben. Sie

sind über Treiber-Bausteine mit mindestens 24mA

Low-Signalstrom (z.B. ’LS245, ’LS373, ’LS374) auf die

Leitungen zu geben.

KoppK: (Kopplungssignal)

BusyK: (Busy Kopplung)

LFTK: (Lifetime Kopplung)

Diese Signale gehören dem Kopplungs-Bus an und werden

zusammen mit der Kopplungskarte beschrieben (Siehe Kopplungskarte <-> Interface-Steuerungen.).

Tab. 7.2.2.1 Schnittstelle zur Datenquelle (IFS-Bus) Signal Funktion Leitung IFS Quelle KPL LFTQ Lifetime 25 c a PrioReqQ\ Vorrang 26 c a GateSQ Gate 27 c a BusyQ\ Busy 28 c a StopQ Stop 29 c a AcceptedQ Data 30 c a RequestQ\ Data Request 31 c a ReadyQ\ Date Ready 32 c a KoppK\ Kopplungssignal 23 a,c a,c a BusyK\ Kopplung 24 a,c a,c a LFTK Lifetime 22 a,c a,c a

Abb. 7.2.2.2 Timing zwischen IFS-Karte und Datenquelle

Nächste: Interface-Steuerung <-> Routing-Steuerung, Vorige: Quellen-Interface <-> Interface-Steuerung, Nach oben: Komponenten und Schnittstellen [Inhalt]

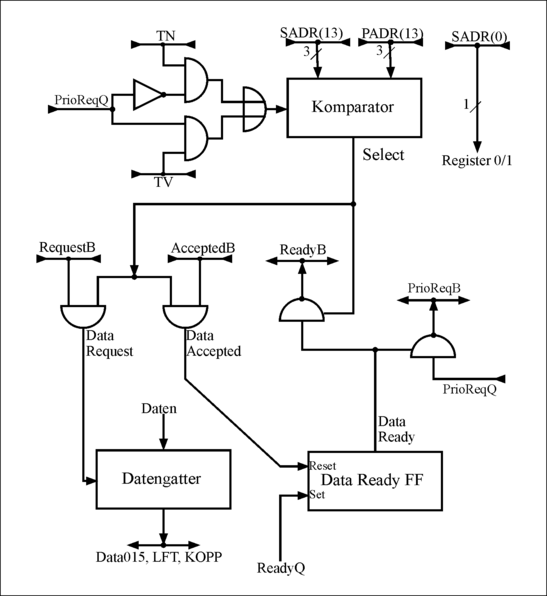

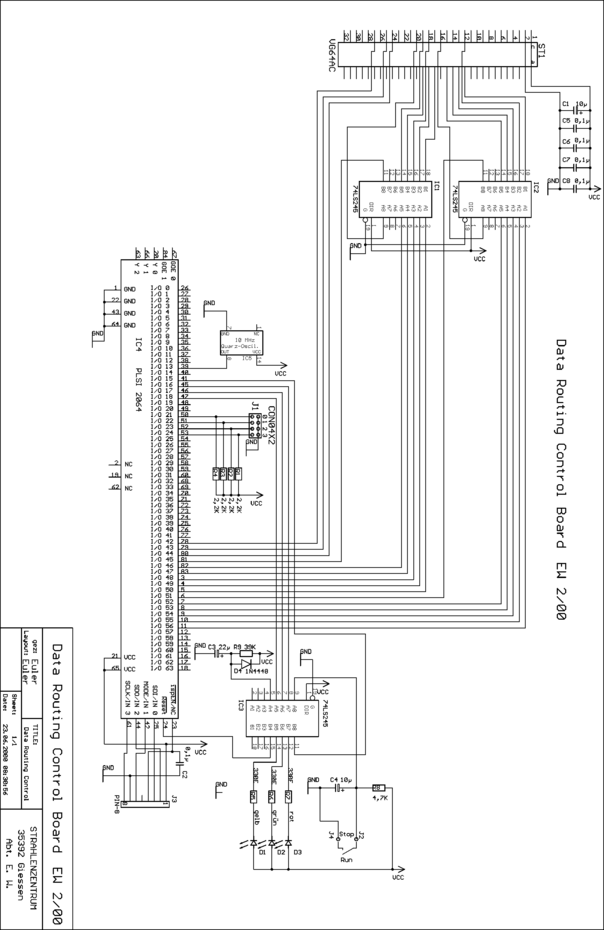

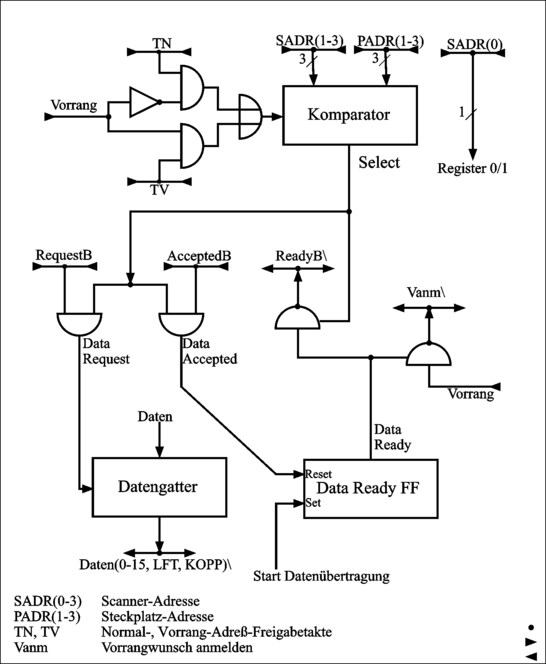

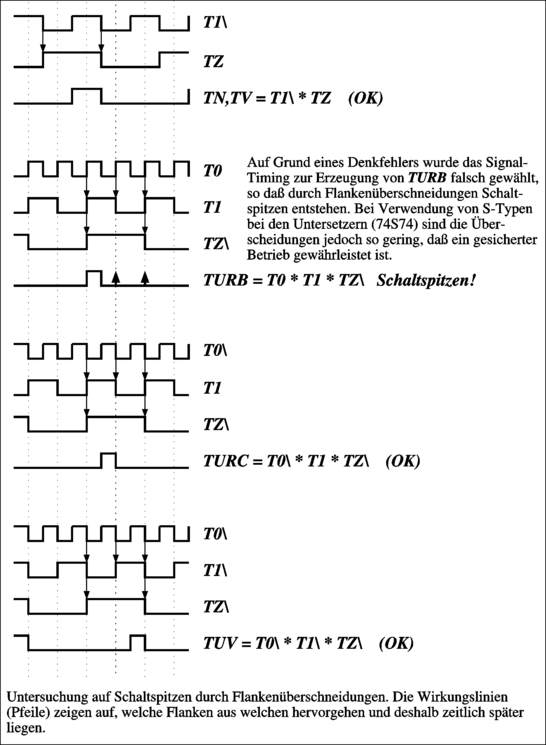

Abb. 7.2.3.1 Interface-Steuerung

Nächste: Routing-Steuerung, Vorige: Interface-Steuerung, Nach oben: Komponenten und Schnittstellen [Inhalt]

Die Routing-Steuerung verständigt sich mit der Interface-Steuerung durch einen Hand-Shake-Dialog über Signalleitungen des Routing-Busses:

Signalnamen ohne Backslash ’\’: aktiv high

Signalnamen mit Backslash ’\’: aktiv low

Ein ’^’ vor dem Signalnamen: die Routing-Steuerung ist die

Quelle des Signals

^10 MHz-Clock,-Clock\

Quarzstabilisierter 10MHz Mastertakt der Routing-Steuerung.

Tastverhältnis: 1:2

Stabilität: 10ppm

^1 MHz-Clock

vom Mastertakt abgeleiteter 1MHz-Takt.

Tastverhältnis: 1:2

^SAddr0..3\ (Scanner-Adresse)

Scanner-Adresse (4 Bits) zur Abfrage der Interface-Steuerungen.

ReadyB\

Die abgefragte Interface-Steuerung meldet sich bei der

Routing-Steuerung mit ReadyB, falls sie ein Datenwort

übertragen will.

^StopB\

Dieses Signal teilt allen Interface-Steuerungen mit, dass die

Routing-Steuerung gestoppt wurde (manuell oder durch Rechner).

^TN, ^TV

Freigabetakte für den Adressvergleich auf den

Interface-Steuerungen für Normal- (TN) bzw.

Vorrangmodus (TV).

PrioReqB\

Anmeldung eines vorrangigen Bearbeitungswunsches bei der

Routing-Steuerung durch die Interface-Steuerungen.

Dieses Signal muss mit ’Open-Collector-Technik’ (wired OR)

beschaltet werden.

Nächste: Routing-Steuerung <-> Rechneranpassung, Vorige: Interface-Steuerung <-> Routing-Steuerung, Nach oben: Komponenten und Schnittstellen [Inhalt]

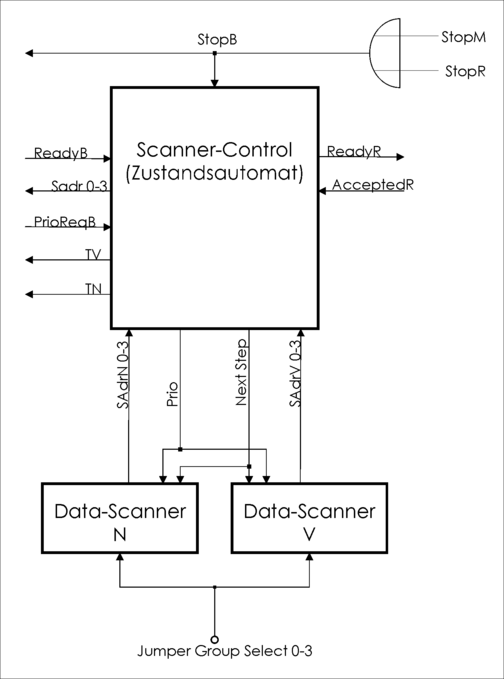

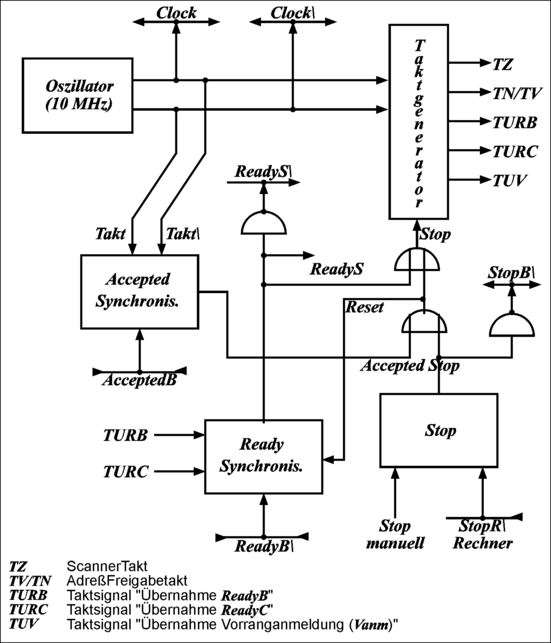

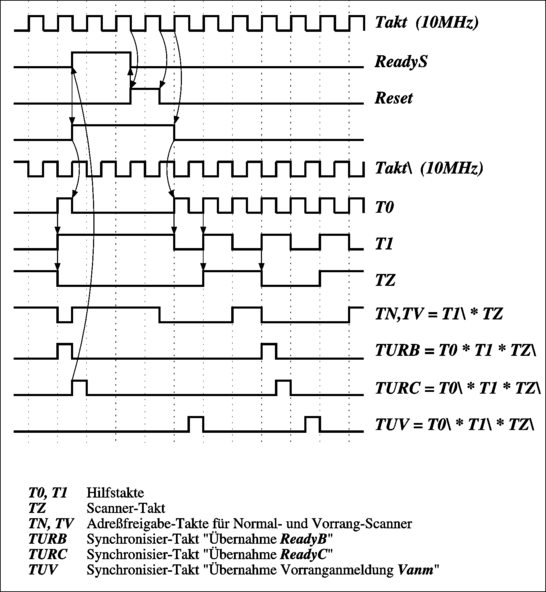

Im Mai 2000 wurde eine Neuentwicklung der Routing-Steuerung fertiggestellt und nach und nach zum Einsatz gebracht. Sie verwendet die alten Frontplatten. Die Schaltung ist im wesentlichen auf einem hochintegrierten, programmierbaren Baustein untergebracht. Ihre Funktionalität und Betriebssicherheit wurden verbessert.

Die Routing-Steuerung ist mit zwei alternativ laufenden Scannern unterschiedlicher Priorität ausgestattet, mit denen die Eingabekanäle abgefragt werden. Sie schickt zu diesem Zweck über vier Bus-Leitungen (SAddr0..3) nacheinander die Scanner-Adressen 0-15 an alle Interface-Steuerungen. Diese vergleichen die drei höchstwertigen Bits der Scanner-Adressen mit ihrer Steckplatzadresse (PAddr1..3), die für jeden Steckplatz fest verdrahtet ist. Bei Gleichheit gilt der Eingabekanal als angewählt und kann bei Bedarf mit der Routing-Steuerung kommunizieren.

Es besteht die Möglichkeit, einen oder mehrere Eingabekanäle mit Vorrang vor den anderen abfragen zu lassen. Dazu müssen diese Eingabekanäle einen Vorrangwunsch (PrioReqB) bei der Routing-Steuerung anmelden, sobald sie bereit sind ein Datenwort zu übertragen. Diese Anmeldung kann zu jeder Zeit asynchron erfolgen. Nach jedem Scanner-Schritt prüft die Routing-Steuerung die PrioReqB-Leitung ab und setzt den Betrieb mit dem gewünschten Scanner (Vorrang- bzw. Normal-Scanner) fort. Der jeweils ruhende Scanner behält seine Position bei, so dass er an der unterbrochenen Stelle weiterlaufen kann. Der im Vorrangmodus arbeitende Eingabekanal muss sich des Freigabetaktes TV bedienen im Gegensatz zu TN für den Normalmodus.

Ein Stop der Routing-Steuerung kann vom Rechner her erfolgen (StopR) oder über einen Schalter auf der Frontplatte (StopM). Beide bewirken ein Anhalten der Daten-Scanner. Ferner wird der Stop den Eingabekanälen mitgeteilt (StopB) und über die Interface-Steuerung den Datenquellen (StopQ).

Da das gleichzeitige Schalten aller Scanner-Adress-Bits zu massiven Störungen auf dem Routing-Bus geführt hat (einzelne 10MHz Takte wurden verstümmelt), ist die Folge der Scanner-Adressen so gewählt, dass sich stets nur möglichst wenig Bits gleichzeitig ändern. Da die IFS1-Karte das niederwertigste Bit als Clock-Signal verwendet, muss dieses eine 0-1-0 Folge haben. Unter dieser Voraussetzung und der Forderung nach der Möglichkeit für einen verkürzten Scanner-Umlauf, war eine Beschränkung auf 2-Bit-Wechsel möglich.

Die Scanner-Adressen sind in vier Gruppen zusammengefasst, die sich am Anfang und Ende auch gegenüber einigen anderen Gruppen nur um maximal zwei Bits unterscheiden. Sie können deshalb in Einer-, Zweier- und Vierer-Kombinationen verknüpft werden.

Gruppe 0, Adressen 0 - 3

0 0 0 0

0 0 0 1

0 0 1 0

0 0 1 1

Gruppe 1, Adressen 4 - 7

0 1 1 0

0 1 1 1

0 1 0 0

0 1 0 1

Gruppe 3, Adressen 12 - 15

1 1 0 0

1 1 0 1

1 1 1 0

1 1 1 1

Gruppe 2, Adressen 8 - 11

1 0 1 0

1 0 1 1

1 0 0 0

1 0 0 1

Erlaubte Kombinationen von Gruppen mit maximal 2-Bit-Wechsel sind:

0, 1, 2, 3, 0-1, 0-2, 1-3, 2-3, 0-1-3-2

Bei unzulässigen Kombinationen, und falls kein Jumper gesetzt ist, wird 0-1-3-2 ausgeführt.

Es ist zu beachten, dass die verschiedenen Eingabekanäle von der Routing-Steuerung nicht nach einem ’first in - first out’ Verfahren bearbeitet werden, sondern durch einen Scanner reihum abgefragt werden. Dies kann zur Folge haben, dass die einzelnen Eingabekanäle nicht in der Reihenfolge zum Rechner übertragen werden, in der sie zur Übertragung bereit waren. Die damit zusammenhängenden Probleme der Verkoppelung von Datenquellen z.B. bei Koinzidenzexperimenten sind jedoch berücksichtigt (Siehe Kopplungskarte <-> Interface-Steuerungen.).

Da den 4 Bits der Scanner-Adresse nur 3 Bits der Steckplatzadresse gegenüberstehen, kann das niederwertigste Bit der Scanner-Adresse zur Adressierung zweier Register verwendet werden. Die Standard-Interface-Steuerung (IFS-Karte) macht bei der Lifetime-Messung von dieser Möglichkeit Gebrauch.

Die von der Interface-Steuerung zugeführten Signale ReadyB und PrioReqB werden sorgfältig einsynchronisiert , so dass sie asynchron zu den internen Vorgängen auftreten dürfen.

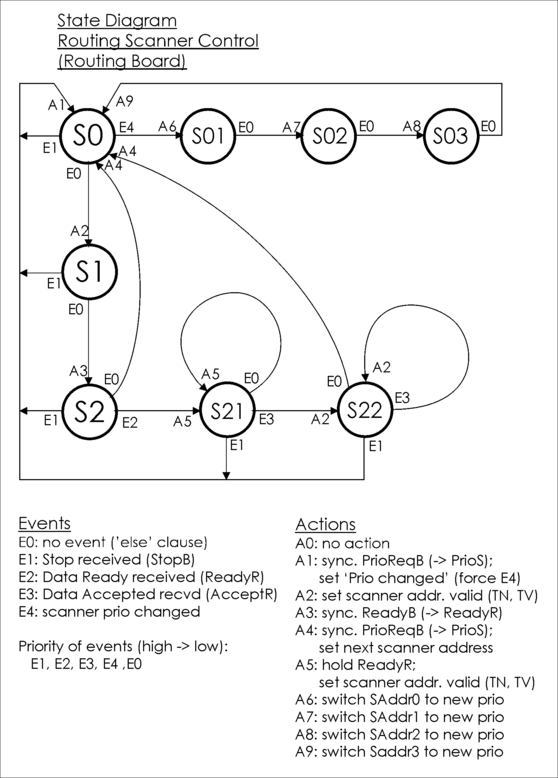

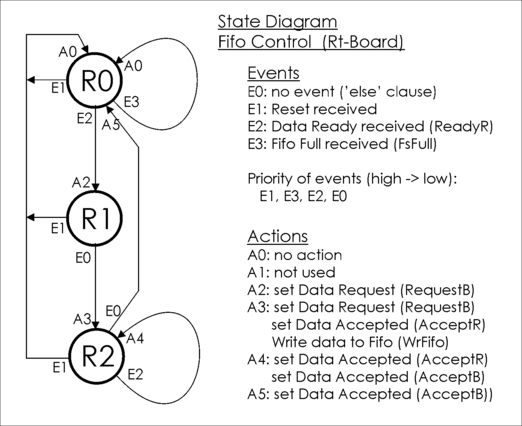

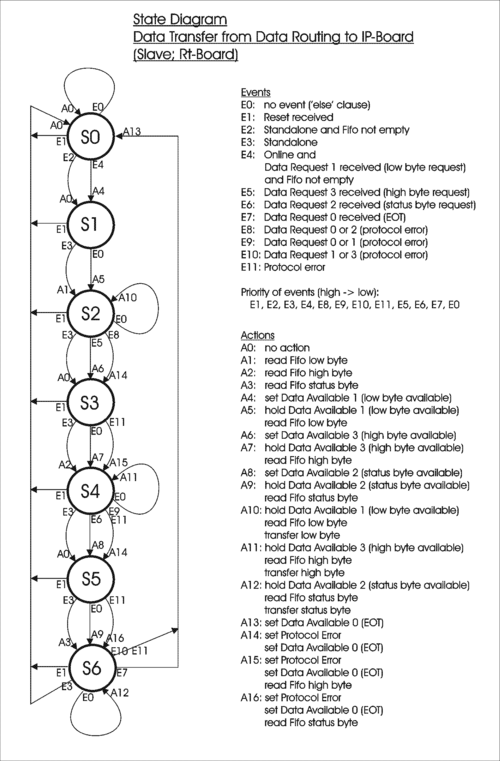

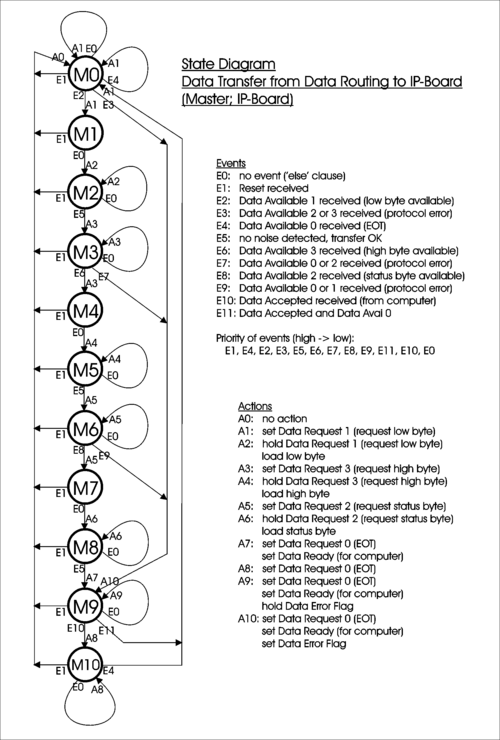

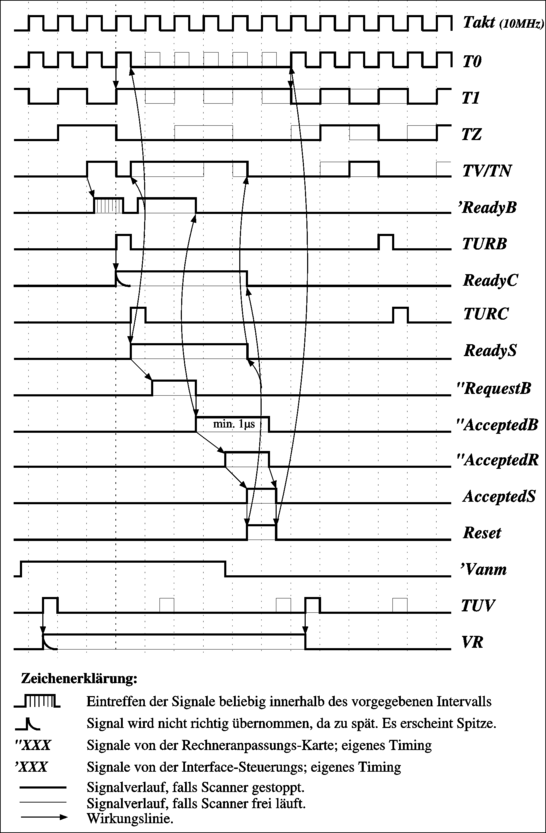

Das Protokoll mit den Eingabekanälen und der Rechneranpassung ist auf der Routing-Steuerung als Zustandsautomat realisiert (Abb. 7.2.5.1, 7.2.5.2):

Bei der Rückkehr nach Z0 wird die nächste Scanner-Adresse geschaltet und das Vorrangsignal (PrioReqB) einsynchronisiert (A4).

Ferner wird ReadyR an die Rechneranpassung weitergegeben zur Anmeldung einer Datenübertragung. Sobald die Rechneranpassung bereit ist, ein Datenwort aufzunehmen, meldet sie sich mit einem Data-Request-Signal (RequestB) und veranlasst damit ein Öffnen der Datengatter des angewählten Eingabekanals (Quellen-Interface). Aus den 16 Daten-Bits, dem LFT- und Kopp-Bit und den 4 Bits der Scanner-Adresse setzt die Rechneranpassung ein Datenwort zusammen (Siehe »Rechneranpassung«.) und überträgt es zum Rechner. Der Empfang der Daten wird von der Rechneranpassung mit den Data-Accepted-Signalen AcceptedB und AcceptedR quittiert. Auf der Routing-Steuerung bewirkt die Rückflanke von AcceptedR ein Weiterstarten des Daten-Scanners unabhängig davon ob ReadyB noch ansteht oder nicht. Die Datenquelle wird durch AcceptedB im allgemeinen zu einer Normierung veranlasst, zur Vorbereitung auf das nächste Datenwort.

In Z21 wird auf das Data Accepted (AcceptedR) der Rechneranpassung gewartet und in Z22 auf dessen Ende.

Bei der Rückkehr nach Z0 wird die nächste Scanner-Adresse geschaltet und das Vorrangsignal (PrioReqB) einsynchronisiert (A4).

Timing:

Der Zustandsautomat wird mit 10MHz getaktet. Daraus ergibt sich folgendes Timing

(zum Vergleich die Werte für die ausgemusterte Routingsteuerung).

| neu | alt | ||

| Adressfortschaltung im Leerlauf | A = | 300ns | 400ns |

| Datenübertragung | D = | 400ns | 500ns |

| Scanner-Prioritätswechsel | P = | 400ns | 0ns |

| 4 Gruppen, 1 Sanner-Umlauf: | |||

| Leerlauf | (16A) | 4800ns | 6400ns |

| 1 Prio 0 Datenübertragung | (16A + D) | 5200ns (192kHz) | 7100ns (141kHz) |

| 1 Prio 1 Datenübertragung | (16A + 2P + D) | 6000ns (167kHz) | 7100ns (141kHz) |

| 2 Gruppen, 1 Sanner-Umlauf: | |||

| Leerlauf | (8A) | 2400ns | |

| 1 Prio 0 Datenübertragung | (8A + D) | 2800ns (357kHz) | |

| 1 Prio 1 Datenübertragung | (8A + 2P + D) | 3600ns (278kHz) | |

| 1 Gruppe, 1 Sanner-Umlauf: | |||

| Leerlauf | (4A) | 1200ns | |

| 1 Prio 0 Datenübertragung | (4A + D) | 1600ns (625kHz) | |

| 1 Prio 1 Datenübertragung | (4A + 2P + D) | 2400ns (417kHz) |

Abb. 7.2.5.1 Routingsteuerung

Abb. 7.2.5.2 Zustandsdiagramm Scanner Control

Abb. 7.2.5.3a Data Transfer Timing IFS1 Board / Control Board / Routing Board Prio 0: (RtBoard Firmware 1.2, Hardware-Aenderung 1.2a) ns 0 100 200 300 400 500 600 700 800 900 0 100 200 300 400 500 600 700 25ns ..|...|...|...|...|...|...|...|...|...|...|...|...|...|...|...|...|...|... Clock \_/^\_/^\_/^\_/^\_/^\_/^\_/^\_/^\_/^\_/^\_/^\_/^\_/^\_/^\_/^\_/^\_/^\_/^\_ PrioReqB __________________________________________________________________________ TN ______/^^^\___/^^^^^^^^^^^^^^^\___/^^^\_______/^^^\_______/^^^\___________ TV __________________________________________________________________________ ReadyB _______/^^^\___/^^^^^^^^^^^^^^^\__________________________________________ ReadyR __________/^^^^^^^^^^^\___________________________________________________ RequestB ______________/^^^^^^^\___________________________________________________ AcceptR __________________/^^^^^^^\_______________________________________________ AcceptB ______________________/^^^^^^^\___________________________________________ 25ns ..|...|...|...|...|...|...|...|...|...|...|...|...|...|...|...|...|...|... ns 0 100 200 300 400 500 600 700 800 900 0 100 200 300 400 500 600 700 States S 0 1 2 21 21 22 22 0 1 2 0 1 2 0 1 2 0 States R 0 0 0 1 2 2 0 0 0 0 0 0 0 0 0 0 0

Abb. 7.2.5.3b Data Transfer Timing IFS1 Board / Control Board / Routing Board Prio 0: (RtBoard Firmware 1.2, ohne Hardware-Aenderung 1.2a) ns 0 100 200 300 400 500 600 700 800 900 0 100 200 300 400 500 600 700 25ns ..|...|...|...|...|...|...|...|...|...|...|...|...|...|...|...|...|...|... Clock \_/^\_/^\_/^\_/^\_/^\_/^\_/^\_/^\_/^\_/^\_/^\_/^\_/^\_/^\_/^\_/^\_/^\_/^\_ PrioReqB __________________________________________________________________________ TN ______/^^^\___/^^^^^^^^^^^^^^^^^^^^^^^\___/^^^\_______/^^^\_______/^^^\___ TV __________________________________________________________________________ ReadyB _______/^^^\___/^^^^^^^^^^^^^^^^^^^^^^^\__________________________________ ReadyR __________/^^^^^^^^^^^^^^^\_______________________________________________ RequestB ______________/^^^^^^^\___________________________________________________ AcceptR ______________________/^^^^^^^^^^^\_______________________________________ AcceptB ______________________/^^^^^^^^^^^\_______________________________________ 25ns ..|...|...|...|...|...|...|...|...|...|...|...|...|...|...|...|...|...|... ns 0 100 200 300 400 500 600 700 800 900 0 100 200 300 400 500 600 700 States S 0 1 2 21 21 21 22 22 22 0 1 2 0 1 2 0 1 2 States R 0 0 0 1 2 2 2 0 0 0 0 0 0 0 0 0 0 0