[Inhalt]

(Schnittstelle zur Experimentkontrolle)

April 1995 K. Huber, Strahlenzentrum Univ. Gießen

Version 11.Oct.2024

| • Einleitung | ||

| • Aufbau und Funktion | ||

| • Standardkomponenten | ||

| • Standard-Interface-Karten | ||

| • Spezielle Interface-Karten | ||

| • Zählratenstatistik | ||

| • Technische Details | ||

| • Oldies |

Nächste: Aufbau und Funktion, Nach oben: Top [Inhalt]

Zur Datenerfassung und Experimentsteuerung existieren zwei verschiedene Rechner-Interfaces, das Data-Routing und das Control-Routing, so genannt nach den Aufgaben, zu denen sie im Wesentlichen eingesetzt werden:

Die vorliegende Funktionsbeschreibung befasst sich

ausschließlich mit dem Control-Routing. Es wird im folgenden oft

abgekürzt als Routing bezeichnet.

Für das Data-Routing existiert eine eigene Beschreibung.

Das Kapitel Aufbau und Funktion gibt einen Überblick über den Aufbau des Control-Routing.

Das Kapitel Standardkomponenten enthält die Aufgabenbeschreibungen und Bedienungsanleitungen der Standardkarten des Routing.

Das Kapitel Standard-Interface-Karten enthält die Aufgabenbeschreibungen und Bedienungsanleitungen der Routing-Karten, die allgemein bei Experimenten zum Einsatz kommen.

Das Kapitel Spezielle Interface-Karten enthält eine Aufstellung der Routing-Karten, die für einzelne Experimente entwickelt wurden. Ihre Beschreibung findet man i.a. in den Unterlagen der Experimente, bei denen sie eingesetzt werden.

Das Kapitel Technische Details gibt technische Detail-Informationen über die Komponenten und deren Schnittstellen.

Im Kapitel Oldies sind überholte Beschreibungen gesammelt.

Nächste: Standardkomponenten, Vorige: Einleitung, Nach oben: Top [Inhalt]

| • Aufbau des Routing | ||

| • Überrahmen |

Nächste: Ueberrahmen, Nach oben: Aufbau und Funktion [Inhalt]

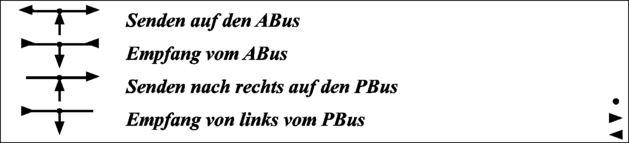

Abb.: Datentransfer mit dem Control-Routing-System

Vorige: Aufbau des Routing, Nach oben: Aufbau und Funktion [Inhalt]

Das Control-Routing ist in einem 19"-Überrahmen untergebracht

mit 20 Steckplätzen für Europakarten

(Siehe Abb Routing-Ueberrahmen.).

Es wird der

gleiche Überrahmen wie für das Data-Routing verwendet. In

Ausnahmefällen können Data-Routing und Control-Routing im gleichen

Überrahmen untergebracht werden, wenn die Bus-Verdrahtung in

der Mitte durchtrennt wird und für die zweite Hälfte ein

Bus-Abschluss nachgerüstet wird.

Die Routing Back-Plane enthält 42 allgemeine Bus-Leitungen für

die Routing-Steuerung und 11 Privat-Bus-Leitungen zur

Kommunikation benachbarter Karten.

Außer der Spannungsversorgung sind alle Schaltungskomponenten

auf steckbaren Karten untergebracht.

Als Steckverbindung zum Routing-Bus werden 64-polige VG-Stecker verwendet. Die Anschlüsse der VG-Leisten sind im Überrahmen zum Teil als durchgehender Bus verdrahtet (allg. Bus: 1a,1c,...,21c) und zu einem anderen Teil bestehen Verbindungen zu benachbarten Steckerleisten (Privat-Bus: 22a/c,...,32a/c) (Siehe Routing-Bus.). Ferner ist für jede Leiste von links beginnend eine Steckplatzkodierung von 0-7 verdrahtet, wobei jedoch jeweils zwei benachbarte Leisten die gleiche Kodierung haben. Die vier überbleibenden Steckplätze am rechten Ende erhalten alle die Kodierung 7. Sie sind vorzugsweise für die Rechner-Anpassung und Routing-Steuerung zu benutzen, da der Bus-Abschluss sich am linken Ende des Überrahmens befindet. Am äußersten rechten Ende ist die Netzkarte mit Netzschalter und Betriebsspannungsanzeigen fest installiert.

Die Frontplattenbreite für eine Steckkarte ist üblicherweise 20 mm, es stehen jedoch auch 40 und 50 mm Frontplatten zur Verfügung.

Achtung:

Es wird dringend empfohlen, die Frontplatten der Steckkarten

mit dem Überrahmen zu verschrauben zur Vermeidung von

Betriebsstörungen. Bitte die Schrauben nicht gewaltsam

anziehen, da dies zur Zerstörung der Gewinde im Überrahmen

führt. Schrauben von min. 10mm Länge verwenden, sonst besteht

ebenfalls die Gefahr der Zerstörung der Gewinde.

Abb.: Routing-Überrahmen

Steckplatz

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20

+--+--+--+--+--+--+--+--+--+--+--+--+--+--+--+--+--+--+--+--+--+

| | | | | | | | | | | | | | | | | | |RS|RA|SV|

| | | | | | | | | | | | | | | | | | | | | |

| | | | | | | | | | | | | | | | | | | | | |

| | | | | | | | | | | | | | | | | | | | | |

+--+--+--+--+--+--+--+--+--+--+--+--+--+--+--+--+--+--+--+--+--+

0 0 1 1 2 2 3 3 4 4 5 5 6 6 7 7 7 7 7 7

Steckplatzkodierung

RS = Routingsteuerung

RA = Rechneranpassung

SV = Spannungsversorgung

Nächste: Standard-Interface-Karten, Vorige: Aufbau und Funktion, Nach oben: Top [Inhalt]

| • Rechneranpassung und Routing-Steuerung | ||

| • Address-Decoder |

Nächste: Address-Decoder, Nach oben: Standardkomponenten [Inhalt]

Diese beiden Funktionen sind entweder auf einer gemeinsamen Karte oder auf zwei benachbarten Karten, mit der Steuerung links und der Anpassung rechts, untergebracht.

| • Rechneranpassung | ||

| • Routing-Steuerung |

Nächste: Routing-Steuerung, Nach oben: Rechneranpassung und Routing-Steuerung [Inhalt]

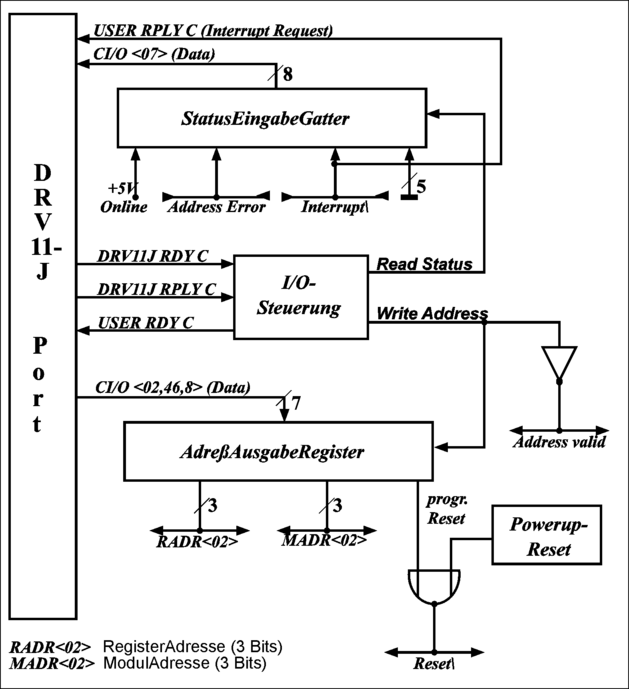

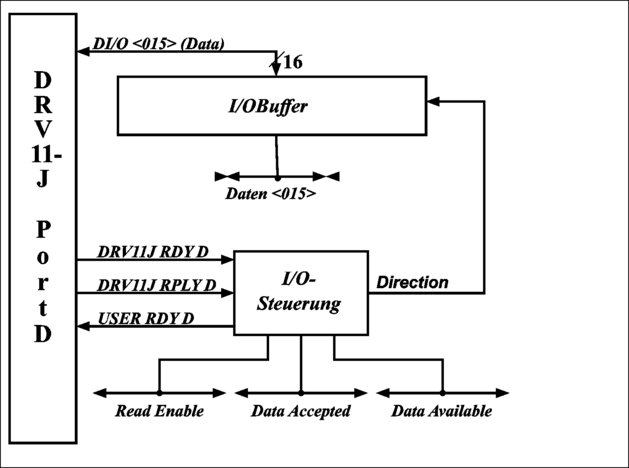

Die Rechneranpassungs-Karte enthält Sender, Empfänger und eventuell Pegelwandler für die Dialog- und Datenleitungen zwischen dem Rechner und dem Routing.

Bisher wurden drei Anpassungen an verschiedene Host-Rechner realisiert:

Vorige: Rechneranpassung, Nach oben: Rechneranpassung und Routing-Steuerung [Inhalt]

Die Routing-Steuerung ist das logische Interface zwischen den

rechnerseitigen Signalen und dem Routing-Bus. Sie kontrolliert

den Datentransfer mit den Registern der Experiment-Interfaces

und sammelt deren Interruptanforderungen, um sie an den Rechner

weiterzuleiten.

Die Control-Routing-Steuerung besitzt keine Bedienungselemente.

Siehe Aufbau des Routing.

Siehe Komponenten und Schnittstellen.

Vorige: Rechneranpassung und Routing-Steuerung, Nach oben: Standardkomponenten [Inhalt]

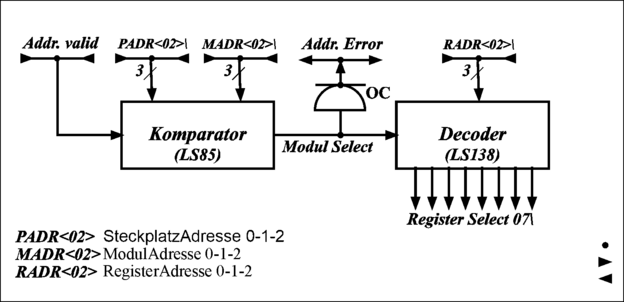

Zur Erleichterung des Anschlusses von Experiment-Interfaces wurde eine standardisierte Karte zur Entschlüsselung der binär verschlüsselten Modul- und Register-Adressen entwickelt. Die Address-Decoder-Karte belegt eine Steckplatz abhängige Moduladresse (3 Bits) und entschlüsselt die zugehörigen Registeradressen (3 Bits). Über den P-Bus (VG-Stecker Pins 22c - 29c; Siehe Routing-Bus.) gibt sie 8 Register-Select-Signale an rechts nachfolgende Experiment-Interfaces weiter. Ihr Einsatz kann entfallen, wenn die Experiment-Interfaces die Entschlüsselung selber vornehmen.

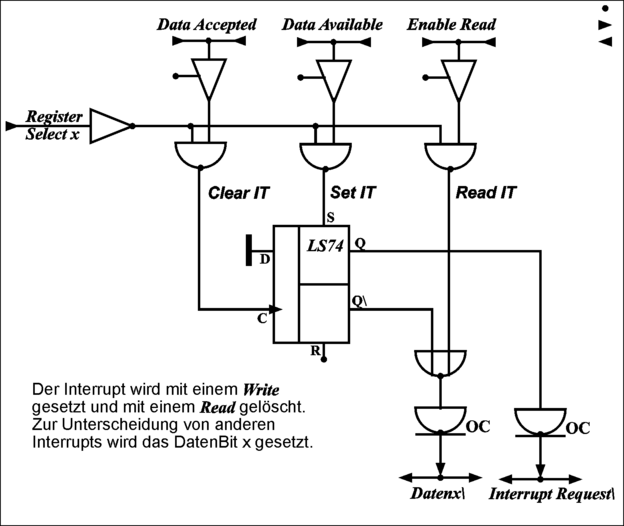

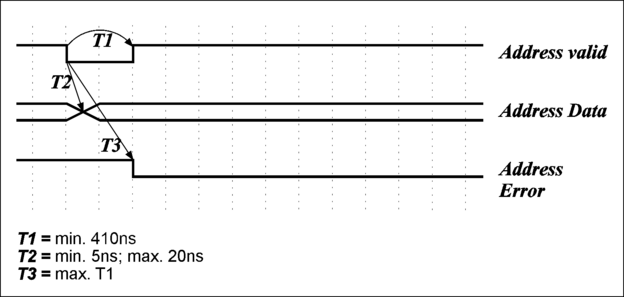

Sobald das Signal "Address valid" anliegt, vergleicht die Address-Decoder-Karte ihre Steckplatzadresse PADR<0-2> mit der aktuellen Moduladresse MADR<0-2>. Bei Gleichheit aktiviert sie einen 3 zu 8 Demultiplexer, der aus der codierten Registeradresse RADR<0-2> 8 einzelne Register-Select-Signale erzeugt (Siehe Aufbau des Routing.), die sie über den P-Bus (Siehe Routing-Bus.) den benachbarten Experiment-Interfaces zur Verfügung stellt.

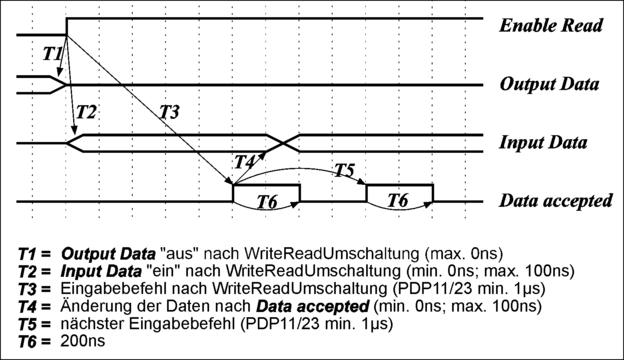

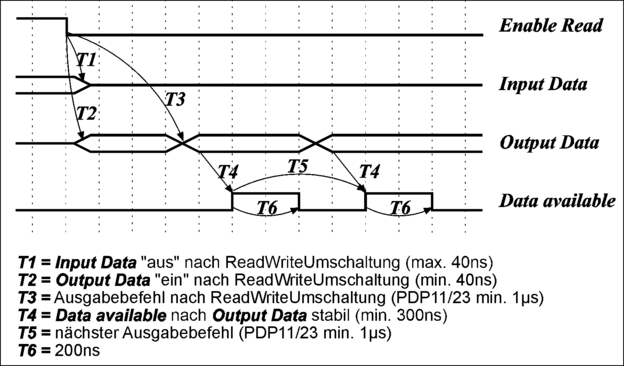

Die über den P-Bus angeschlossenen Experiment-Interfaces nutzen die Register-Select-Signale zusammen mit den Routing-Bus-Signalen "Enable Read", "Data Accepted" und "Data Available" zur Steuerung der Ein- und Ausgabe von Daten.

Es existieren zwei Versionen der Address-Decoder-Karte, die sich in den Bedienungselementen und Anzeigen und zum Teil auch in der Funktion unterscheiden:

Bedienungselemente:

alte Version:

Schalter: Run/Stop

Run : Die Address-Decodierung ist in Betrieb

Stop: Die Address-Decodierung ist außer Betrieb und alle

Register-Select-Signale sind abgeschaltet (high).

neue Version: keine Bedienungselemente

Anzeigen:

alte Version:

LED : Select

LED leuchtet: Address-Decoder-Karte ist durch Moduladresse selektiert

LEDs: 4 2 1

Anzeige der Steckplatzadresse

LED leuchtet: Bit der angegebenen Wertigkeit ist gesetzt

neue Version:

LEDs: 0 1 2 3 4 5 6 7

Register select

LED n leuchtet: Register n ist selektiert

LEDs: 4 2 1

Anzeige der Steckplatzadresse

LED leuchtet: Bit der angegebenen Wertigkeit ist gesetzt

Funktionelle Unterschiede:

alte Version:

Ursprünglich war geplant, dass das "Address_Error"-Signal

(Routing-Bus VG-Stecker Pin 16c) von jedem Experiment-Interface

gelöscht wird, dessen Register adressiert werden. Tatsächlich

wurde jedoch auf der alten Address-Decoder-Version "Address_Error"

bereits gelöscht, wenn diese über die Moduladresse angesprochen

wurde, und die Experiment-Interfaces haben möglicherweise

das "Address_Error"-Signal nicht bedient. Damit kann jedoch

die Software nicht feststellen, ob eine benötigte

Experiment-Interface-Karte fehlt oder defekt ist. Durch

Auftrennen der Verbindung nach Pin 16c auf dem Address-Decoder

ist diese Panne zu beheben. Dann müssen gegebenenfalls

aber die Experiment-Interfaces nachgerüstet werden (s.u.).

neue Version:

Die neue Address-Decoder Version überlässt das Löschen des

"Address_Error"-Signals den Experiment-Interfaces, die dann

zum Teil

aber nachgerüstet werden müssen (teilweise bereits

geschehen), falls die Software "Address_Error" abprüft.

Nachrüstung:

Als Nachrüstung genügt eine Diode vom Eingang der

verwendeten "Register Select"-Signale zum Ausgang

des "Address_Error"-Signals, z.B.:

22c ---|<|--- 16c

Nächste: Spezielle Interface-Karten, Vorige: Standardkomponenten, Nach oben: Top [Inhalt]

Nächste: Serielle Ausgabe, Nach oben: Standard-Interface-Karten [Inhalt]

Dieses PSO14 Control Routing Board ist ein neuentwickelter Parallel-Seriell-Wandler mit Ausgabe der seriellen Signale über Lichtleiter, der die G. Hoffmann Wandler zur Steuerung der Netzgeräte der neuen e-Kanone im Labor 017 ersetzt. Er kann mit unterschiedlicher Firmware programmiert werden um damit die alten Hofmann-Module (z.B. DAC-Karten) steuern zu können oder die neuentwickelten, seriellen AD5541CR oder LTC2758 DAC-Karten.

| • Serielle Protokolle | ||

| • PSO2 Firmware | ||

| • PSO32 Firmware | ||

| • LWL-Planung | ||

| • Probleme und Lösungen |

Nächste: PSO2 Firmware, Nach oben: Serielle Ausgabe (PSO14) [Inhalt]

| • Original Hofmann Protokoll | ||

| • Modifizierte Hofmann Protokolle | ||

| • PSO16/32 Protokolle |

Nächste: MHProtokoll, Nach oben: Protokolle (PSO14) [Inhalt]

Im Hofmann Protokoll wiederholen die PSO-Karten nach einer kurzen

Pause beständig ihre Ausgabe. Nach dem Anschalten starten die Karten

sofort mit der Ausgabe der zunächst undefinierten Information.

Erhalten sie über das Control Routing neue Daten so wird die

laufende Ausgabe abgebrochen und eine neue wird gestartet.

Der serielle Empfänger erkennt den Abbruch und verwirft die unvollständigen

Daten. Dies führt bei zu rasch aufeinander folgender Eingabe neuer Daten

dazu, dass die serielle Ausgabe niemals fertig wird.

Die serielle Ausgabe wird mit 32.768kHz oder 2.4576 MHz getaktet. Ein Bit ist 8 Takte lang. Nach 16 Bits oder einem Abbruch folgt eine 8 Takte lange Pause. Bit = 0: 1 1 0 0 0 0 0 0 Bit = 1: 1 1 1 1 1 0 0 0 Pause : 0 0 0 0 0 0 0 0 LSB wird zuerst gesendet.

Nächste: PSO16/32 Protokolle, Vorige: OHProtokoll, Nach oben: Protokolle (PSO14) [Inhalt]

Es stehen zwei leicht unterschiedliche Versionen zur Verfügung, mit denen versucht wird die Schwächen des Originals zu umgehen:

Die serielle Ausgabe wird nur mit 2.4576 MHz getaktet. Ein Bit ist 8 Takte lang. Nach 16 Bits oder einem Abbruch folgt eine 8 Takte lange Pause. Bit = 0: 1 1 0 0 0 0 0 0 Bit = 1: 1 1 1 1 1 0 0 0 Pause : 0 0 0 0 0 0 0 0 LSB wird zuerst gesendet.

Vorige: MHProtokoll, Nach oben: Protokolle (PSO14) [Inhalt]

Die PSO16/32 Protokolle übertragen 16 bzw. 32 Bit serielle Daten. Sie werden zum Steuern der neuen AD5541CR (16 Bit) und LTC2758 DAC-Karten (32 Bit) benötigt. Sie sind NICHT kompatibel mit vorhandenen Hofmann DAC-Karten.

Bit-Takt: 2.5000 MHz Header : 101010101010101 Daten : xxxxxxxxxxxxxxxx/xxxxxxxxxxxxxxxx

Nächste: PSO32 Firmware, Vorige: Protokolle (PSO14), Nach oben: Serielle Ausgabe (PSO14) [Inhalt]

Mit der PSO2 Firmware können die beiden LWL-Sender unabhängig von einander programmiert und betrieben werden. Die PSO2 Firmware existiert in zwei Versionen (PSO2V1 und PSO2V4) mit den unterschiedlichen, modifizierten Hofmann Protokollen PSO2V1 bzw. PSO2V4. Jede dieser Versionen kann durch Steckbrücken für einen Hofmann kompatiblen Modus (MODE = old) oder einen AD5541CR DAC-Karten kompatiblen Modus (MODE = new) konfiguriert werden.

| • Bedienelemente (PSO2) | ||

| • Programmierung (PSO2) |

Nächste: Programmierung (PSO2), Nach oben: PSO2 Firmware [Inhalt]

LED "Busy " : Anzeige einer Schreiboperation LWL-Buchse 0 : serieller Lichtleiter-Ausgang 0 LWL-Buchse 1 : serieller Lichtleiter-Ausgang 1 Brücke Mode 0: Stecker für Modus old/new Kanal 0 Brücke Mode 1: Stecker für Modus old/new Kanal 1 TP Word 0 : Triggersignal für Start einer seriellen Ausgabe 0 TP Bit 0 : Triggersignal für Bits einer seriellen Ausgabe 0 TP Word 1 : Triggersignal für Start einer seriellen Ausgabe 1 TP Bit 1 : Triggersignal für Bits einer seriellen Ausgabe 1

Vorige: Bedienelemente (PSO2), Nach oben: PSO2 Firmware [Inhalt]

Mit der PSO2 Firmware belegt die PSO14-Karte zwei Registeradressen des Address-Decoders mit doppelter Funktion:

Register 0 : Statusabfrage Kanal 0 / Ausgabe Datenwort Kanal 0 Register 1 : Statusabfrage Kanal 1 / Ausgabe Datenwort Kanal 1

Statusabfrage:

Beim Adressieren des Registers antwortet der zugeordnete

Kanal nur mit einem Address-Accepted (AddAcc) wenn er nicht busy ist.

Dieses Signal kann über den Routing-Status abgefragt werden:

Eingabe ((Routing Status & 0x0008) != 0) -> Kanal busy

Diese Statusabfrage ist nur bei Verwendung einer neuen Address-Decoder-Karte (EW 3/04) möglich da die alten (EW 21-88) ebenfalls dieses Bit bedienen (Siehe Address-Decoder.). Auf den alten gegebenenfalls die 16c-Verbindung zum VG-Stecker auftrennen. Für Interface-Karten, die AddAcc nicht bedienen führt dies aber zu einer Fehlermeldung falls die Software AddAcc abprüft!

Daten Ausgabe:

Die 16 Daten-Bits werden in dem zugeordneten Datenregister gespeichert

und die Parallel-Seriell-Wandlung gestartet.

Nächste: LWL-Planung (PSO14), Vorige: PSO2 Firmware, Nach oben: Serielle Ausgabe (PSO14) [Inhalt]

Mit der PSO32 Firmware können die beiden LWL-Sender unabhängig von einander für das PSO16 oder PSO32 Protokoll programmiert und betrieben werden zur Kontrolle der neuen AD5541CR (16 Bit) und LTC2758 DAC-Karten (32 Bit). Da geplant ist, die AD5541CR-Karten auf das 32 Bit Protokoll umzuprogrammieren, wird das 16 Bit Protokoll möglicherweise in Zukunft nicht mehr gebraucht...

| • Bedienelemente (PSO32) | ||

| • Programmierung (PSO32) |

Nächste: Programmierung (PSO32), Nach oben: PSO32 Firmware [Inhalt]

LED "Busy " : Anzeige einer Schreiboperation LWL-Buchse 0 : serieller Lichtleiter-Ausgang 0 LWL-Buchse 1 : serieller Lichtleiter-Ausgang 1 Brücke Mode 0: unbenutzt Brücke Mode 1: unbenutzt TP Word 0 : Triggersignal für Start einer seriellen Ausgabe 0 TP Bit 0 : Triggersignal für Bits einer seriellen Ausgabe 0 TP Word 1 : Triggersignal für Start einer seriellen Ausgabe 1 TP Bit 1 : Triggersignal für Bits einer seriellen Ausgabe 1

Vorige: Bedienelemente (PSO32), Nach oben: PSO32 Firmware [Inhalt]

Mit der PSO32 Firmware belegt die PSO14-Karte zwei Registeradressen des Address-Decoders mit doppelter Funktion:

Register 0 : Statusabfrage Kanal 0 / Kommando Ausgabe Register 1 : Statusabfrage Kanal 1 / Daten Ausgabe

Statusabfrage:

Beim Adressieren des Registers antwortet der zugeordnete

Kanal nur mit einem Address-Accepted (AddAcc) wenn er nicht busy ist.

Dieses Signal kann über den Routing-Status abgefragt werden:

Eingabe ((Routing Status & 0x0008) != 0) -> Kanal busy

Diese Statusabfrage ist nur bei Verwendung einer neuen Address-Decoder-Karte (EW 3/04) möglich da die alten (EW 21-88) ebenfalls dieses Bit bedienen (Siehe Address-Decoder.). Auf den alten gegebenenfalls die 16c-Verbindung zum VG-Stecker auftrennen. Für Interface-Karten, die AddAcc nicht bedienen führt dies aber zu einer Fehlermeldung falls die Software AddAcc abprüft!

Kommando Ausgabe:

unteres Nippel -> Kanal 0, oberes Nippel -> Kanal 1 Bit wenn gesetzt: 0/4 1 -> nächste 16 Bit Datenausgabe auf low-Register 1/5 1 -> nächste 16 Bit Datenausgabe auf high-Register 2/6 0/1 -> 16/32 Bit Mode 3/7 1 -> Start des Kanals 0/1 z.B. 0xAD -> Start Kanal 0, Mode32, nächstes Laden: low-Register Start Kanal 1, Mode16, nächstes Laden: high-Register

Daten Ausgabe:

Die 16 Daten-Bits werden gemäß der Kommando-Bits

in den Datenregistern gespeichert. Die Daten bleiben auch nach einer

seriellen Übertragung erhalten.

Nächste: Probleme und Loesungen (PSO14), Vorige: PSO32 Firmware, Nach oben: Serielle Ausgabe (PSO14) [Inhalt]

Die Leistung der LWL-Sender SFH756V muss an die Leitungslänge und die Empfindlichkeit der Empfänger SFH551V angepasst werden. Bisher wurden die Sender nahezu mit voller Leistung betrieben, was bei kurzen Leitungen (<2m) zu Übersteuerung der Empänger führt. Rechnungen mit Hilfe der Datenblätter und Application Notes und Tests zeigen, dass statt des bisher verwendeten Vorwiderstands von 82 Ohm eher 330 Ohm geeignet sind um bei Zimmertemperatur Leitungslängen von 1.5 m bis 20 m sicher abzudecken. Bei Tests mit den AD5541CR DAC-Boards waren die Grenzen ca. 82 Ohm bei 1.20 m und 2.5 kOhm bei 10 m.

Bezug: 1mW -> 0db

Rechnung für max Leitungslänge (sicherer Betrieb nach Application Notes)

Fiber length [m] 30,00 20,00 10,00 5,00

Detector power (min=-17db, max=-6db) [db] -17,00 -17,00 -17,00 -17,00

Fiber attenuation (0.22db/m) [db] 6,60 4,40 2,20 1,10

Additional fiber attanuation (0.5db/m) [db] 1,50 1,50 1,50 1,50

Aging of fiber and known link disadvantages [db] 1,00 1,00 1,00 1,00

Aging of transmitter and receiver [db] 2,00 2,00 2,00 2,00

Range of emitter power due to temperature [db] 3,00 3,00 3,00 3,00

Min emitter power (max 0db) [db] -2,90 -5,10 -7,30 -8,40

LED current [mA] 26,68 16,54 10,25 8,07

Resistor at 3V [kOhm] 0,112 0,181 0,29 0,372

Rechnung für min Leitungslänge ohne Übersteuerung des Empfängers

Fiber length [m] 3,00 2,00 1,50 1,00

Detector power (min=-17db, max=-6db) [db] -6,00 -6,00 -6,00 -6,00

Fiber attenuation (0.22db/m) [db] 0,66 0,44 0,33 0,22

Additional fiber attanuation (0.5db/m) [db] 1,50 1,00 0,75 0,50

Aging of fiber and known link disadvantages [db] 0,00 0,00 0,00 0,00

Aging of transmitter and receiver [db] 0,00 0,00 0,00 0,00

Range of emitter power due to temperature [db] 0,00 0,00 0,00 0,00

Angstfaktor [db] -3,00 -3,00 -3,00 -3,00

Max emitter power (max 0db) [db] -6,84 -7,56 -7,92 -8,28

LED current [mA] 11,33 9,69 8,96 8,29

Resistor at 3V [kOhm] 0,265 0,310 0,335 0,362

Rechnung für max Leitungslänge (sicherer Betrieb bei Zimmertemperatur)

Fiber length [m] 30,00 20,00 10,00 5,00

Detector power (min=-17db, max=-6db) [db] -17,00 -17,00 -17,00 -17,00

Fiber attenuation (0.22db/m) [db] 6,60 4,40 2,20 1,10

Additional fiber attanuation (0.5db/m) [db] 1,50 1,50 1,50 1,50

Aging of fiber and known link disadvantages [db] 1,00 1,00 1,00 1,00

Aging of transmitter and receiver [db] 2,00 2,00 2,00 2,00

Range of emitter power due to temperature [db] 0,00 0,00 0,00 0,00

Min emitter power (max 0db) [db] -5,90 -8,10 -10,30 -11,40

LED current [mA] 13,90 8,62 5,34 4,21

Resistor at 3V [kOhm] 0,216 0,348 0,562 0,713

Vorige: LWL-Planung (PSO14), Nach oben: Serielle Ausgabe (PSO14) [Inhalt]

Störungen beim Abschalten der PSO-Karte

Im Testbetrieb zeigte sich, dass beim

Abschalten des Überrahmens die PSO-Karte für einige ms

periodische Signale sendet, die auf den DAC-Karten zu

Zufallswerten führen. Eine genauere Untersuchung ergab,

dass offenbar der 74LS245 als Treiber für die LWL-Sender

diese Oszillationen erzeugt.

Wegen dieser Oszillationen beim Abschalten war die neue PSO-Karte zum Betrieb von Hofmann-DACs (Mode = old), obwohl dafür geplant, nicht geeignet. Deshalb wurde der LS245 probehalber ersetzt durch ein Piggy-Board mit BC556 Transistoren:

LS245 IN --> BC556-Basis LS245 OUT --> BC556-Emitter LS245 VCC --> BC556-Collector

Diese Schaltung vermeidet die Oszillationen, hat aber flachere Flanken als ein LS245. Mit den neuen DAC-Boards ist das kein Problem. Aber die DAC-Karten in der Spannungsregelung von W. Arnold haben eine heftige, periodische Störung, die bei den LWL-Empfängern zu Einbrüchen in den Flanken und damit zu Übertragungsfehlern führt.

Die verschiedenen 245 Typen zeigen unterschiedliches Verhalten beim Abschalten:

Fairchild, Motorola Typen: Typ Oszillationen Pause Nachleuchten LS245 120 kHz / 1.5 ms 8 ms 4 ms ALS245 2-3 MHz / 200 us -- 4 ms HC245 70 kHz / 2.3 ms -- 23 ms HCT245 70 kHz / 3 ms -- 20 ms Hingegen keine Oszillationen bei Texas Instrument Typen: LS245, LS645, ALS245

Alle PSO-Karten sind jetzt mit SN74ALS245AN bestückt.

Die Oszillationen beim Abschalten waren der Anlass, das

Übertragungs-Protokoll völlig zu überarbeiten.

Nachdem zunächst versucht wurde, auch im Mode = new möglichst

das Hofmann-Protokoll zu verwenden, hat es nun mit dem ursprünglichen

Hofmann-Protokoll keine Verwandschaft mehr:

Zuerst wird ein 15 Bit langes festes Muster (101010101010101) als Header

gesendet, auf das sich die DAC-Karte synchronisiert. Dann folgen nahtlos

die 16/32 Daten-Bits. Damit konnten die Oszillationen beim Abschalten

sehr sicher erkannt werden da die Bit-Frequenz (2.5Mhz, 400ns) sich

wesentlich von der Störung unterscheidet. Eine vollständige 16 Bit

Übertragung braucht ca. 13us und ist damit ca. vier mal schneller

als das Hofmann-Protokoll.

Danach zeigte sich, dass die PSO-Karte beim Abschalten noch zum Senden

eines regulären Datenwortes angeregt wird mit der Info 0xffff, was

bei den DACs zu 10V Ausgang führt.

Mit der PSO2Vx Firmware konnte dies nur dadurch verhindert werden, dass

die PSO-Karte 0xffff niemals senden darf. Der letzte 0.15mV Schritt kann

also nicht eingestellt werden.

Mit der PSO32 Firmware wird dies verhindert durch das Pruefen des MSB

auf 0 im Kommando.

Nächste: Serielle Eingabe, Vorige: Serielle Ausgabe (PSO14), Nach oben: Standard-Interface-Karten [Inhalt]

| • Aufgabe, Funktion | ||

| • Bedienelemente | ||

| • Programmierung | ||

| • Asynchrones, serielles Protokoll von G. Hoffmann |

Nächste: Bedienelemente (PSO), Nach oben: Serielle Ausgabe [Inhalt]

Diese Parallel-Seriell-Wandlerkarte wurde von G. Hoffmann entworfen. Sie wird bei verschiedenen Experimenten zur Steuerung eingesetzt: z. B. e-Kanonen-Netzgeräte, Messbereichs-Einstellungen usw..

Ein 16 Bit Datenwort wird seriell gewandelt und auf 50 Ohm Koax-Leitung ausgegeben. Die serielle Ausgabe wiederholt sich beständig. Sie wird abgebrochen und neu gestartet, wenn ein neues 16 Bit Datenwort ausgegeben wird. Dies schein aber nicht bei allen Karten reibungslos zu funktionieren (s.u.). Die Karten können, dem Problem angepasst, mit zwei unterschiedlichen internen Takten betrieben werden (32.768kHz, 2.4576MHz) und die Bits invertiert oder nicht invertiert senden.

Von der Parallel-Seriell-Wandlerkarte existieren zur Zeit mehrere unterschiedliche Layouts (Schaltungsunterlagen im 017-Ordner):

Layout 0 (20/88):

???

Layout 1 (26/88):

modifiziertes Layout 0, davon gibt es möglicherweise nur ein Exemplar;

interner Takt fest, nur mit einem Quarz bestückt;

Lötbrücken zum Umpolen der Ausgänge.

Layout 2 (26/88):

verbessertes Layout 1, häufiger im Einsatz;

interner Takt fest, nur mit einem Quarz bestückt;

manche Exemplare machen Probleme (s.h. 017-Ordner),

wenn die Ausgabe eines Datenwortes schneller erfolgt als die Dauer

des seriellen Signals (4.395ms bei 32.768kHz), sie senden

überwiegend Schrott;

Lötbrücken zum Umpolen der Ausgänge.

Layout 3 (29.08.94; 13/96):

neues Layout;

zwei Quarze für 32.768kHz und 2.4576MHz interne Takte,

wählbar über Steckbrücke;

Steckbrücke zum Umpolen der Ausgänge.

Die Serielle Ausgabe belegt eine Registeradresse des Address-Decoders (Siehe Address-Decoder.).

Nächste: Programmierung (PSO), Vorige: Funktion (PSO), Nach oben: Serielle Ausgabe [Inhalt]

Layout 0: ???

Layout 1: LED "Write" : Anzeige einer Schreiboperation BNC-Buchsen : serielles Ausgangssignal, nicht kurzschlussfest 2 Brücken : Polarität des Ausgangssignals

Layout 2: LED "Write" : Anzeige einer Schreiboperation BNC-Buchsen : serielles Ausgangssignal, nicht kurzschlussfest 2 Brücken : Polarität des Ausgangssignals

Layout 3: LED "Busy" : Anzeige einer Schreiboperation LED "2MHz" : Anzeige 2.4576MHz Betrieb LED "32kHz" : Anzeige 32.768kHz Betrieb LED "Q" : Ausgangssignal normal LED "Q\" : Ausgangssignal invertiert BNC-Buchsen : serielles Ausgangssignal, nicht kurzschlussfest Brücke "Q/Q\" : Polarität des Ausgangssignals Brücke "2.4576MHz/32.768kHz": Taktwahl

Nächste: Protokoll (PSO), Vorige: Bedienelemente (PSO), Nach oben: Serielle Ausgabe [Inhalt]

Register 0 out: auszugebendes Datenwort (16 Bits)

Vorige: Programmierung (PSO), Nach oben: Serielle Ausgabe [Inhalt]

Nächste: Parallele Ausgabe, Vorige: Serielle Ausgabe, Nach oben: Standard-Interface-Karten [Inhalt]

| • Aufgabe, Funktion | ||

| • Bedienelemente | ||

| • Programmierung |

Nächste: Bedienelemente (SPI), Nach oben: Serielle Eingabe [Inhalt]

Diese Seriell-Parallel-Wandlerkarte wurde von G. Hoffmann entworfen. Sie wird bei verschiedenen Experimenten zur Statuseingabe eingesetzt: z. B. Messbereichs-Einstellungen der Ionenstrom-Konverter usw..

Ein seriell über 50 Ohm Koax-Leitung eingegebenes Signal wird parallel in ein 16 Bit Datenwort gewandelt. Die Karten können, dem Problem angepasst, mit zwei unterschiedlichen internen Takten betrieben werden (32.768kHz, 2.4576MHz). Dazu muss der Quarz ausgetauscht werden.

Von der Seriell-Parallel-Wandlerkarte existieren zur Zeit mehrere unterschiedliche Layouts (11/88, 19/88, 3/89).

Nächste: Programmierung (SPI), Vorige: Funktion (SPI), Nach oben: Serielle Eingabe [Inhalt]

Layout 3/89:

LED "Read" : Anzeige einer Leseoperation

BNC-Buchse : serielles Eingangssignal

(TTL, G. Hoffmann Protokoll, 50 Ohm Abschluss)

Vorige: Bedienelemente (SPI), Nach oben: Serielle Eingabe [Inhalt]

Register 0 in: Eingabe des Datenwort (16 Bits)

Nächste: Messintervall Timer, Vorige: Serielle Eingabe, Nach oben: Standard-Interface-Karten [Inhalt]

| • Aufgabe, Funktion | ||

| • Bedienelemente | ||

| • Programmierung |

Nächste: Bedienelemente (PPO), Nach oben: Parallele Ausgabe [Inhalt]

Diese Karte für Parallele Ausgabe wurde von G. Hoffmann entworfen. Sie wird bei Scan-Experimenten in den Labors 017 und SI zur Ausgabe der aktuellen Kanalnummer eingesetzt.

Ein 16 Bit Datenwort wird parallel auf einen 20-poligen Flachbandstecker ausgegeben. Für diese Karte gibt es kein eigenes Layout sondern es wird ein modifiziertes 26/88-Layout des Parallel-Seriell-Wandlers verwendet (handverdrahtet). Ein Redesign wäre gelegentlich angebracht.

Die Parallele Ausgabe belegt eine Registeradresse des Address-Decoders (Siehe Address-Decoder.).

Nächste: Programmierung (PPO), Vorige: Funktion (PPO), Nach oben: Parallele Ausgabe [Inhalt]

LED "Write" : Anzeige einer Schreiboperation

20-pol. Flachbandstecker: parallele Ausgangssignale (16 Bits, TTL)

Bit Pin Bit Pin

00 17 08 04

01 15 09 06

02 13 10 08

03 11 11 10

04 09 12 12

05 07 13 14

06 05 14 16

07 03 15 18

Ground 1,2 Ground 19,20

Vorige: Bedienelemente (PPO), Nach oben: Parallele Ausgabe [Inhalt]

Register 0 out: auszugebendes Datenwort (16 Bits)

Nächste: Programmierbare Zeitbasis, Vorige: Parallele Ausgabe, Nach oben: Standard-Interface-Karten [Inhalt]

| • Aufgabe, Funktion | ||

| • Bedienelemente | ||

| • Programmierung |

Nächste: Bedienelemente (MIT), Nach oben: Messintervall Timer [Inhalt]

Diese Timer-Karte wurde von G. Hoffmann entworfen. Sie wird bei Scan-Experimenten in den Labors 017 und SI zur Programmierung der Mess- und Pausen-Intervalle der einzelnen Scan-Schritte eingesetzt.

Zur Zeit existieren 2 handverdrahtete Karten, die noch im Einsatz sind, und einige Eagle-geroutete Karten.

Der Messintervall Timer belegt eine Registeradresse des Address-Decoders (Siehe Address-Decoder.).

Nächste: Programmierung (MIT), Vorige: Funktion (MIT), Nach oben: Messintervall Timer [Inhalt]

LED "Write" : Anzeige einer Schreiboperation LED "Intervall" : Anzeige Messintervall aktiv BNC-Buchse "Intervall" : Messintervall Ausgang, TTL, pos. Logik BNC-Buchse "Intervall\" : Messintervall Ausgang, TTL, neg. Logik BNC-Buchse "ext. Takt" : externer Takt Eingang, TTL BNC-Buchse "ext. Start" : externer Start Eingang, TTL, pos. Logik

Vorige: Bedienelemente (MIT), Nach oben: Messintervall Timer [Inhalt]

Register 0 out: Timer Datenwort (16 Bits)

Bit 15 1 = externer Takt

Bit 14 1 = nur externer Start

Bits (12..8) Exponent E = 0...31

Bits (7..0) Mantisse M = 0...255

Zeitintervall = M * 2^E * T

T (Taktperiode) = 1 us für internen Takt

Berechnung von M und E für ein Intervall mit x Takten:

( ld(x) = ld(10) * lg(x) = 1 / lg(2) * lg(x) )

E = MAX(0, INT( ld(x)) -7)

M = INT(x / 2^E) (max .8% Abweichung)

M = INT(x / 2^E + 0.5) (max .4% Abweichung)

Beispiele für internen 1 MHz Takt:

Intervall M E Datenwort

1us (1 us) 1 0 0x0001

10us (10 us) 10 0 0x000a

100us (100 us) 100 0 0x0064

1ms (1 ms) 250 2 0x02fa

10ms (9.984 ms) 156 6 0x069c

100ms (99.84 ms) 195 9 0x09c3

1s (0.999424 s) 244 12 0x0cf4

10s (10.02701 s) 153 16 0x1099

Interner/externer Start:

Bit 14 ext Start Write Intervall-Start

0 H ja ja

0 L ja nein

0 L->H -- ja

1 L -- nein

1 H -- nein

1 L->H -- ja

Nächste: Interrupt Eingabe, Vorige: Messintervall Timer, Nach oben: Standard-Interface-Karten [Inhalt]

| • Aufgabe, Funktion | ||

| • Bedienelemente | ||

| • Programmierung |

Nächste: Bedienelemente (PZB), Nach oben: Programmierbare Zeitbasis [Inhalt]

Diese Zeitbasis-Karte wurde von G. Hoffmann entworfen. Sie wird in den Labors 017 und SI zur Registrierung der Messzeit pro Kanal eingesetzt.

Sie stellt den 2^n-fach untersetzten (n=0..15, programmierbar) internen 1 MHz Quarztakt am Ausgang zur Verfügung.

Es existieren verschiedene Layouts dieser Karte: 36/88, 2/89, 15/97

Die Programmierbare Zeitbasis belegt eine Registeradresse des Address-Decoders (Siehe Address-Decoder.).

Nächste: Programmierung (PZB), Vorige: Funktion (PZB), Nach oben: Programmierbare Zeitbasis [Inhalt]

LED "Write" : Anzeige einer Schreiboperation LEDs "8 4 2 1" : Anzeige von "n" der 2^n-Taktuntersetzung BNC-Buchse "Out" : untersetzter Zeittaktausgang, TTL

Vorige: Bedienelemente (PZB), Nach oben: Programmierbare Zeitbasis [Inhalt]

Register 0 out: Zeitbasis Datenwort (16 Bits)

Bits (3..0) n=0..15 für Untersetzung 1/2^n des 1MHz Taktes

Nächste: Programmierbare Totzeit, Vorige: Programmierbare Zeitbasis, Nach oben: Standard-Interface-Karten [Inhalt]

| • Aufgabe, Funktion | ||

| • Bedienelemente | ||

| • Programmierung |

Nächste: Bedienelemente (ITR), Nach oben: Interrupt Eingabe [Inhalt]

Diese Karte wurde von G. Hoffmann entworfen. Sie wird in den Labors 017 und SI bei den Scan-Experimenten zur Synchronisierung des Experimentablaufs durch Interrupt eingesetzt.

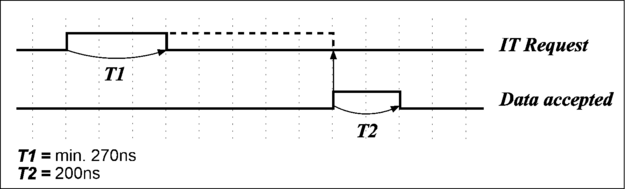

Das Experiment startet die Karte mit dem Startimpuls (Start-Eingang). Gleichzeitig wird der Busy-In-Eingang mit der Summe aller relevanter Busy-Signale versorgt. Erst wenn das Summen-Busy verschwunden ist wird die Karte aktiv und gibt sowohl einen Interrupt-Wunsch an den Rechner ein, als auch ein Steuersignal (Read/Reset) an das Experiment aus.

Je nach Konfiguration (Steckbrücke J2) gibt die Karte nur einen Interrupt-Impuls an den Rechner oder sie speichert den Interrupt-Wunsch bis er durch eine Leseoperation gelöscht wird. Letztere Konfiguration wird benötigt, wenn mehrere Interrupt-Quellen existieren und durch Lesen der zugehörigen Register herausgefunden werden muss, welcher Interrupt aktiv war. Ein Interrupt steht an und wird gelöscht, wenn beim Lesen das Daten-Bit 0 gesetzt ist.

Es existieren verschiedene Layouts dieser Karte: 01.08.94, 11/97

Die Interrupt-Karte belegt eine Registeradresse des Address-Decoders (Siehe Address-Decoder.). Sie kann jedoch im IT-Puls-Modus ohne Address-Decoder betrieben werden.

Nächste: Programmierung (ITR), Vorige: Funktion (ITR), Nach oben: Interrupt Eingabe [Inhalt]

LED "Select" : Anzeige, dass die Karte adressiert ist

LED "Interrupt" : Anzeige für einen anstehenden Interrupt

LED "Busy" : Anzeige des Busy-Signals vom Experiment

BNC-Buchse "Start" : Eingabe des Startsignals, TTL, pos. Logik

BNC-Buchse "Read/Reset": Ausgabe eines Steuersignals für das Experiment,

TTL, 100ns, pos. Logik

BNC-Buchse "Busy\ in" : Eingabe des Busy-Signals vom Experiment,

TTL, neg. Logik

BNC-Buchse "Busy out" : Ausgabe des Busy-Signals vom Experiment,

TTL, pos. Logik

Steckbrücke J2/1-2 : Die IT-Karte meldet mit einem IT-Puls einen

Interrupt bei der Routing-Steuerung an. Die

IT-Karte benötigt dann keine Address-Decoder-

Karte und der IT kann nicht gelesen werden.

Steckbrücke J2/2-3 : Die IT-Anmeldung wird auf der IT-Karte

gespeichert und solange an die Routing-Steuerung

gemeldet, bis er durch einen Read auf Register 0

(Bit 0) gelesen und gelöscht wird.

Vorige: Bedienelemente (ITR), Nach oben: Interrupt Eingabe [Inhalt]

Register 0 in: Lesen und Löschen des Interrupts

Bit 0 1 = es steht ein Interrupt an

Nächste: CAN Controller, Vorige: Interrupt Eingabe, Nach oben: Standard-Interface-Karten [Inhalt]

| • Aufgabe | ||

| • Funktion | ||

| • Bedienelemente | ||

| • Programmierung | ||

| • Messungen | ||

| • Totzeit-Rechnungen | ||

| • Anwendungen |

Nächste: Funktion (PDT), Nach oben: Programmierbare Totzeit [Inhalt]

Gelegentlich kann die exakte Totzeit einer Apparatur nicht bestimmt werden, so dass notwendige Korrekturrechnungen nicht möglich sind. In diesem Falle empfiehlt sich das Vorschalten einer gut bekannten künstlichen Totzeit, die über alle anderen Totzeiten der Apparatur dominiert, und deshalb als einzige in die Korrektur eingeht.

Manche Detektoren (z.B. Channeltrons) neigen dazu, nach einem registrierten Ereignis weitere Impulse abzugeben, durch die eine Messung erheblich verfälscht werden kann. Durch eine Totzeit können solche Nachimpulse unterdrückt werden. Dabei ist jedoch zu beachten, dass eine nicht-paralysierende Totzeit wie man sie z.B. mit einem Pulse-Strecher realisieren könnte in einem solchen Falle nicht ausreichend ist.

Beachten Sie dazu den Abschnitt »Anwendungen«.

Zur Untersuchung des Ereignisstromes auf Totzeiten, Nachimpulse usw. existiert eine Interface-Karte zum Messen der Abstandsverteilung von Impulsen, zu der es eine Anleitung in der Data-Routing-Funktionsbeschreibung gibt: HTML-Version, PDF-Version.

Nächste: Bedienelemente (PDT), Vorige: Aufgabe (PDT), Nach oben: Programmierbare Totzeit [Inhalt]

Die Totzeitkarte kann sowohl über das Control-Routing als auch manuell (Jumper) programmiert werden in Schritten der Taktperiode. Für die zur Zeit zur Verfügung stehenden Logikbausteine sind Takte bis zu 40 MHz möglich. Standard ist 20 MHz. Es genügt nicht, den Quarzoszillator auszutauschen, der Logikbaustein muss auch umprogrammiert werden, da dieser sonst einen falschen Status meldet. Bei manueller Programmierung spielt dies keine Rolle, die Software würde aber u.U. eine falsche Totzeit einstellen.

Die Totzeitkarte liefert wahlweise eine paralysierende oder nicht-paralysierende Totzeit.

Da die Totzeitkarte digital mit einem Quarztakt T arbeitet ist die Totzeit auf +-T/2 unscharf im Mittel jedoch recht genau (besser 10**-3) (Siehe Mittlere Totzeit.).

Die Totzeitkarte belegt drei Registeradressen des Address-Decoders (Siehe Address-Decoder.).

Nächste: Programmierung (PDT), Vorige: Funktion (PDT), Nach oben: Programmierbare Totzeit [Inhalt]

| LED "Select": | leuchtet, wenn eines der drei Register adressiert wird | |

| BNC-Buchse "In": | Signaleingang (TTL, pos. Logik) | |

| BNC-Buchse "Out": | Signalausgang (TTL, pos. Logik) | |

| BNC-Buchse "Lost": | Ausgang für Totzeitverluste (TTL, pos. Logik) | |

| BNC-Buchse "Deadtime": | Ausgang für Totzeitsignal (TTL, pos. Logik) | |

| manuelle Programmierung: | Siehe Programmierung. |

Nächste: Messungen (PDT), Vorige: Bedienelemente (PDT), Nach oben: Programmierbare Totzeit [Inhalt]

Control-Routing Programmierung:

(dazu muss Jumper J15 entfernt werden!)

Register 0 out: Command

out 0x4000 -> paralysierende Totzeit

out 0x0000 -> nicht-paralysierende Totzeit

Register 0 in: Status

Bit 14 1 = paralysierende Totzeit

Bits (11..4) Taktfrequenz [MHz]

Bits (3..0) Anzahl der Timer Bits (TBITS)

Register 1 out: Ausgangs-Puls-Länge

Bits (TBITS-1..0) Länge Lp in Taktperioden [T]

totale mittlere Pulslänge = (Lp + 2.5) * T

Register 2 out: Länge der Totzeit

Bits (TBITS-1..0) Länge Ld in Taktperioden [T]

totale mittlere Totzeitlänge = (Ld + 3.5) * T

Jumper Programmierung:

(x = Jumper set, - = Jumper not set)

J15 x manuelle (Jumper) Programmierung

J14 x paralysierende Totzeit

- nicht-paralysierende Totzeit

J(13..0) x Länge der Totzeit Ld in Taktperioden [T]

(z.Z. nur J(9..0) belegt!!! ISP-Chip voll)

totale mittlere Totzeit = (Ld + 3.5) * T

totale mittlere Pulslänge = (Ld/2 + 2.5) * T

Pulslänge und Totzeit sind um +-0.5 T unscharf!

(Siehe Mittlere Totzeit.)

Nächste: Totzeit-Rechnungen (PDT), Vorige: Programmierung (PDT), Nach oben: Programmierbare Totzeit [Inhalt]

Der programmierbare Mittelwert der Totzeit ist durch Signallaufzeiten fehlerbehaftet. Der genaue Wert kann mit Doppelpulsgenerator, Oszillograph und passendem Zeitnormal bestimmt werden:

Messung der tatsächlichen Totzeit mit einem Doppelpulser

(Dez. 2001)

Das Scope wurde mit dem Quarz auf dem Deadtime-Board geeicht.

10 MHz Clock

Logikbaustein : ispLSI1032E-70

Clock : 10 MHz

Doppelpulsrate: 15.3 kHz

Doppelpulsabstand (Out - In/2) / In/2

1 300ns .000

2 320ns .130

3 340ns .316

4 360ns .518

5 380ns .718

6 400ns .904

7 420ns 1.00

Fit (Origin) Werte 2 - 6 mit y = a0 + a1 * x

a) a0 = -3.0828 +- .00413

a1 = .01 fest

y = .5 => x = 358.3 +- .4

b) a0 = -2.9928 +- .03141

a1 = .00975 +- .00009

y = .5 => x = 358.3

Totzeit= n * T + 3.5 * T + 8.3ns; T = 100ns; n = prog. Zeit

20 MHz Clock

Logikbaustein : ispLSI1032E-70

Clock : 20 MHz

Doppelpulsrate: 15.3 kHz

(unter 200ns löste der In-Zähler (U/D-Zähler) die Doppelpulse

nur noch teilweise auf, weshalb diese Werte zu hoch ausfallen müssen!)

Doppelpulsabstand (Out - In/2) / In/2

1 150ns .000

2 160ns .045

3 170ns .166

4 180ns .341

5 190ns .572

6 200ns .805

7 210ns 1.00

Fit (Origin) Werte 2 - 6 mit y = a0 + a1 * x

a) a0 = -3.2142 +- .01798

a1 = .02 fest

y = .5 => x = 185.7 +- .9

b) a0 = -3.081 +- .25353

a1 = .01926 +- .0014

y = .5 => x = 185.9

Fit (Origin) Werte 2 - 6 mit y = a0 + a1 * x + a2 * x**2

a) a0 = 3.359 +- 1.08274

a1 = -.05274 +- .01209

a2 = .0002 +- .00003

y = .5 => x = 187.4

Totzeit= n * T + 3.5 * T + 10.7ns; T = 50ns; n = prog. Zeit

Nächste: Anwendungen (PDT), Vorige: Messungen (PDT), Nach oben: Programmierbare Totzeit [Inhalt]

siehe auch Zählratenstatistik:

http://www.strz.uni-giessen.de/ExpHelp/statistik/statistik.html

http://www.strz.uni-giessen.de/ExpHelp/statistik/statistik.pdf

| • Mittlere Totzeit | ||

| • Korrekturformeln für nicht-paralysierende Totzeit | ||

| • Korrekturformeln für paralysierende Totzeit |

Nächste: Nicht-paralysierende Totzeit (PDT), Nach oben: Totzeit-Rechnungen (PDT) [Inhalt]

Da die Totzeitkarte digital mit einem Quarztakt T arbeitet ist die Totzeit auf +-T/2 unscharf. Der Mittelwert liegt etwa bei 0.5T und ist Zählraten abhängig, da eine vorausgehende Totzeit immer mit einem Clock-Tick endet und der Abstand zweier aufeinanderfolgender Pulse eine R * exp(-Rt) -Verteilung hat.

Rechnung für das erste Intervall nach einer Totzeit:

Zeit: t

Clock-Periode: T

Ereignisrate: R

Abstandsverteilung: D(t) = R * exp(-Rt)

Totzeitmittel:

M = Int[0-T]((T - t) * D(t))dt / Int[0-T](D(t))dt

Int[0-T](T * D(t))dt = T * (1 - exp(-RT))

Int[0-T](-t * D(t))dt = -T / RT * (1 - (RT + 1) * exp(-RT))

Int[0-T](D(t))dt = 1 - exp(-RT)

M = T * {1 - [1 - (RT + 1) * exp(-RT)] / [RT * (1 - exp(-RT)]}

RT -> 0: M -> 1/2 * T

RT -> unendl.: M -> 1 * T

RT << 1.0: M ~ (.5 + R*T/12) * T

FM = (M - .5*T)/.5*T = R*T/6

RT = .01: M = .500833 * T

RT = .1: M = .50833 * T

RT = 1.0: M = .5820 * T

Die Korrekturen sind vernachlässigbar;

z.B. 10MHz Clock; 1MHz Rate: 0.8ns Abweichung.

Da die Abstandsverteilung der Pulse eine exp(-Rt) - Verteilung ist, errechnet sich für M bei Eintreffen des nächstfolgenden Pulses in eine der nachfolgenden Clock-Perioden n der gleiche Wert:

D'(t) = R * exp(-R(t+nT)) = D(t) * exp(-RnT) M = Int[0-T]((T - t) * D(t))dt / Int[0-T](D(t))dt

Anm. zur Abstandsverteilung von zufälligen (Poisson-verteilten)

Ereignissen:

Man erhält sie als negative Änderung der Wahrscheinlichkeit, dass

von 0 bis t kein Ereignis eintrifft: ???

D(t) = -d(exp(-Rt) / dt = R * exp(-Rt)

Nächste: Paralysierende Totzeit (PDT), Vorige: Mittlere Totzeit (PDT), Nach oben: Totzeit-Rechnungen (PDT) [Inhalt]

Die Totzeit-Korrekturformeln für konstante, nicht-paralysierende Totzeit sind:

Zeit: t

Clock-Periode: T

In-Rate: R

Out-Rate: r

Totzeitverluste: v

Totzeit: Z

v = r * R * Z

R = r + v = r / (1 - r*Z)

r = R / (1 + R*Z)

Für die unscharfe Totzeit, wie sie die Totzeitkarte liefert, ist eine Mittelung über die auftretenden Totzeiten nötig. Es werden gleichverteilte Totzeiten angenommen:

r' = int[Z1,Z2](r)dZ / int[Z1,Z2]dZ

int[Z1,Z2](r)dZ = ln(1 + R*Z2) - ln(1 + R*Z1)

int[Z1,Z2]dZ = T

r' = 1/T * ln[(1 + R*Z2)/(1 + R*Z1)] (Z1 = Z-T/2; Z2 = Z+T/2)

= 1/T * ln[(1 + R*Z + R*T/2) / (1 + R*Z - R*T/2)]

= 1/T * ln[(1 + R*T/2/(1 + R*Z)) / (1 - R*T/2/(1 + R*Z))]

= 1/T * [ln(1 + r*T/2) - ln(1 - r*T/2)]

rT << 1: r' ~ r * (1 + (r*T)**2 /12)

Fr'= |(r'-r)/r| = (r*T)**2 /12 = (R*T/(1 + R*Z))**2 /12

rT -> 0: r' -> r

R' = (exp(r*T) - 1) / [(Z + T/2) - (Z - T/2)*exp(r*T)]

= (1 - exp(-r*T)) / ((Z + T/2)*exp(-r*T) - (Z - T/2))

rT << 1: R' ~ R/(1 - (r*T)**2 /12)

FR'= |(R'-R)/R| = (r*T)**2 /12 = (R*T/(1 + R*Z))**2 /12

rT -> 0: R' -> R

Die Korrekturen sind vernachlässigbar klein;

z.B. 10MHz Clock; Rate R=1MHz; Totzeit Z=1us: Fr’ = FR’ = .02%

Vorige: Nicht-paralysierende Totzeit (PDT), Nach oben: Totzeit-Rechnungen (PDT) [Inhalt]

Die Totzeit-Korrekturformeln für konstante, paralysierende Totzeit sind:

Zeit: t

Clock-Periode: T

In-Rate: R

Out-Rate: r

Totzeitverluste: v

Totzeit: Z

alle mit kürzerem Abstand als Z gehen verloren

v = R * Int[0,Z](R*exp(-R*Z))

= R * (1 - exp(-R*Z))

r = R - v = R * exp(-R*Z)

R = Umkehrung nur numerisch lösbar und doppeldeutig!

numerische Lösung mit Newton Näherung für R*T < .99:

R = r * (1 + r*Z); /* first approximation */

for(i=0; i<10; i++) {

f = R * exp(-R*Z) - r;

d = exp(-R*Z) * (1 - R*Z);

R = R - f / d; /* Newton */

}

Für die unscharfe Totzeit, wie sie die Totzeitkarte liefert, ist eine Mittelung über die auftretenden Totzeiten nötig. Es werden gleichverteilte Totzeiten angenommen:

v' = int[Z1,Z2](v)dZ / int[Z1,Z2]dZ

int[Z1,Z2](v)dZ = R*(Z2-Z1) + exp(-Z2*R) - exp(-Z1*R)

int[Z1,Z2]dZ = T (Z1 = Z-T/2; Z2 = Z+T/2)

v' = R*[1- 1/(R*T) * exp(-R*Z) * (exp(R*T/2) - exp(-R*T/2))]

r' = R - v' = R * exp(-R*Z) / (R*T) * (exp(R*T/2) - exp(-R*T/2))

= r / (R*T) * (exp(R*T/2) - exp(-R*T/2))

Fr'= |(r'-r)/r| =

= 1/(R*T) * (exp(R*T/2) - exp(-R*T/2)) - 1

RT << 1: Fr' ~ (R*T)**2 /24

Die Korrekturen sind vernachlässigbar klein;

z.B. 10MHz Clock; Rate R=1MHz; Totzeit Z=1us: Fr’ = .04%

R' = Umkehrung nur numerisch lösbar und doppeldeutig!

numerische Lösung mit Newton Näherung für R*T < .99:

R = r * (1 + r*Z); /* first approximation */

for(i=0; i<10; i++) {

f = 1/T * exp(-R*Z) *(exp(R*T/2.) - exp(-R*T/2.)) - r;

d = exp(-R*Z) * (-Z/T*(exp(R*T/2.) - exp(-R*T/2.))

+ 1/2.*(exp(R*T/2.) + exp(-R*T/2.)));

R = R - f / d; /* Newton */

}

Vorige: Totzeit-Rechnungen (PDT), Nach oben: Programmierbare Totzeit [Inhalt]

| • Dominierende Totzeit | ||

| • Beseitigen von Nachimpulsen | ||

| • Beseitigen von Nachimpulsen |

Nächste: Beseitigen von Nachimpulsen, Nach oben: Anwendungen (PDT) [Inhalt]

Gelegentlich sind Totzeiverluste nicht berechenbar da z.B. die Totzeit nicht bekannt oder veränderlich ist. In einem solchen Fall kann mit der "Programmierbaren Totzeit" eine Totzeit erzeugt werden, die die vorausgehenden, unbekannten Totzeiten dominiert.

Hier soll untersucht werden, inwiefern eine dominierende Totzeit geeignet ist, unbekannte Totzeiten so zu überdecken, dass Totzeitkorrekturrechnungen möglich werden.

Wie die folgenden Überlegungen zeigen, kann eine solche dominierende Totzeit nur näherungsweise funktionieren. Die Rechnungen zeigen zeigen in welcher Größenordnung Abweichungen zu erwarten sind und wie man sie eventuell minimieren kann.

Wie Simulationen gezeigt haben, sind die Abweichungen für eine nicht-paralysierende dominierende Totzeit deutlich kleiner als für eine paralysierende.

Nicht-paralysierende dominierende Totzeit

Die primäre Totzeit wird ebenfalls als nicht-paralysierend

und konstant vorausgesetzt.

Für nicht-paralysierende Totzeiten ergibt sich folgendes Verhalten:

E0 E1 E2 E3 En __|____|_____|______|____ T0 __|^^^^^^^^|_____________ Td __|^^^^^^^^^^^^^^^|______ T2 _____________|^^^^^^^^|__ Te __|^^^^^^^^^^^^^^^^^^^|__

Die Totzeitverluste können daher größer sein als die dominierende Totzeit erwarten lässt. Für T0=0 oder Td=T0 ist die Totzeitverlustrechnung Td exakt.

Rechnung

R: Eingangsrate vor allen Totzeiten r: Ausgangsrate nach den Totzeiten r': Ausgangsrate bei T0 = 0 Tp: primäre Totzeit Td: dominierende Totzeit (nicht-paralysierend Vd=R*Td) Vp: zusätzliche Totzeitverluste durch Tp bei Tp < Td Vd: Totzeitverluste durch Td bei Tp = 0

E0 E1 E2 E3 En __|____|_____|______|__________ Tp __|^^^^^^^^^^^|________________ Td __|^^^^^^^^^^^^^^^|____________ Tx ______________|^^^|____________ Tp ________________|^^^^^^^^^^^|__ Ty __________________|^^^^^^^^^|__ Tx = Td - Tp Ty = Tp - Tx/2 Vy = R*Ty * R*Tx = R^2 * (Td-Tp) * (3Tp-Td)/2 für Td = Tp --> Vy = 0 für Td = 2Tp --> Vy = 1/2 * (R*Tp)^2

Paralysierende dominierende Totzeit

Für eine nicht-paralysierende primäre Totzeit und eine

paralysierende dominierende Totzeit ergibt sich folgendes Verhalten:

Durch die primären Verluste von E1 und E3 wird die effektive Totzeit Td zu kurz. Für T0->0 verschwindet dieser Verlust.

E0 E1 E2 E3 En __|____|_____|______|___________ T0 __|^^^^^^^^|____________________ Td __|^^^^^^^^^^|^^^^^^^^^^^^^^^|__ T2 _____________|^^^^^^^^|_________ Te __|^^^^^^^^^^^^^^^^^^^^^^^^^^|__

Rechnung schwierig, noch ungelöst....

Simulationsrechnungen

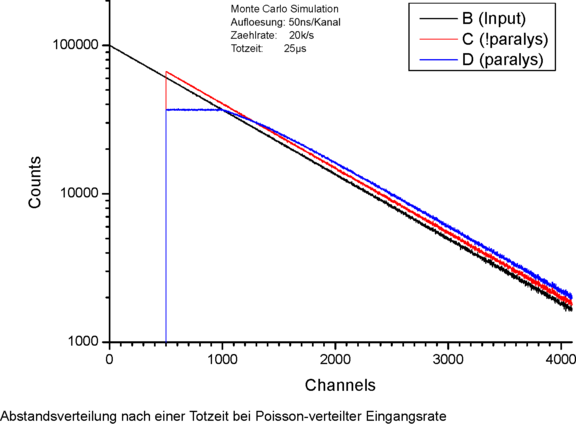

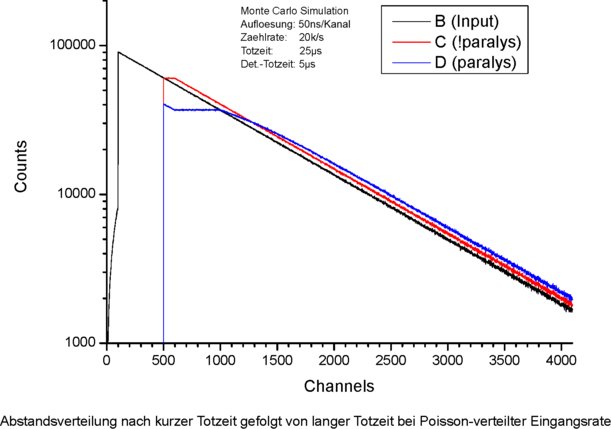

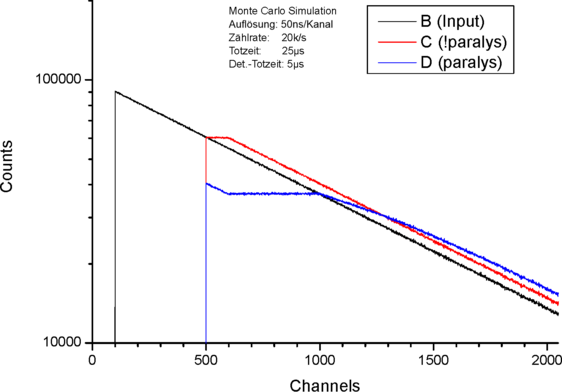

Die folgenden Grafiken sind Ergebnisse von Monte-Carlo-Simulationen,

da für echte Messungen keine ausreichend gute Poisson-verteilte

Ereignisraten zur Verfügung standen. Der Versuch das Ganze mittels

Faltungsintegralen zu berechnen ist ebenfalls an der Komplexität

der Probleme gescheitert.

Sie zeigen die Abstandsverteilungen von Poisson-verteilten Ereignissen nach Durchlaufen von ein bzw. zwei Totzeiten. Wie man sieht haben Totzeiten einen markanten Einfluss auf die Abstandsverteilung und sind nicht nur ein Abschneiden von kurzen Abständen.

Die Abstandsverteilung von Poisson-verteilten Ereignissen ist eine abfallende Exponentialfunktion, in logarithmischer Darstellung also eine Gerade. Eine solche Verteilung lässt sich aus Zufallszahlen leicht herstellen, sodass eine Monte-Carlo-Rechnung ein bequemes Werkzeug zur Untersuchung der Auswirkungen einer Totzeit bei den verschiedenen Anwendungen ist.

wie zuvor, Ausschnitt

Nächste: Beseitigen von Nachimpulsen (PDT), Vorige: Dominierende Totzeit (PDT), Nach oben: Anwendungen (PDT) [Inhalt]

Siehe Zählratenstatisik Doku:

http://www.strz.uni-giessen.de/ExpHelp/statistik/statistik.html

http://www.strz.uni-giessen.de/ExpHelp/statistik/statistik.pdf

Wie man sich leicht überlegen kann, ist die nicht-paralysierende Totzeit nicht geeignet zum Abschneiden von z.B. Nachimpulsen eines Detektors, da nach wie vor beliebig kurze Ereignisabstände auftreten. Die paralysierende Totzeit hingegen entfernt alle Ereignisse, die zu ihrem Vorgänger einen kürzeren Abstand haben als die Totzeit.

Vorige: Beseitigen von Nachimpulsen, Nach oben: Anwendungen (PDT) [Inhalt]

Insbesondere Channeltrons haben die unschöne Eigenschaft nach einem

echten Ereignis noch Nachimpulse zu liefern, die eine

Wirkungsquerschnittmessung deutlich verfälschen können.

Totzeit (500ns) und Nachimpulse (bis ca. 4 us) eines Channeltrons

In dieser logarithmischen Darstellung der Ereignisabstände ist eine

markannte Abweichung von der zu erwartenden Geraden durch die

Poisson-verteilten Ereignisse zu erkennen. Mit einer geeigneten Totzeit

kann der Bereich der Nachimpulse ausgeblendet werden.

Wie man sich leicht überlegen kann, ist die nicht-paralysierende Totzeit

nicht dazu geeignet, da nach wie vor beliebig kurze Ereignisabstände

auftreten können.

Die paralysierende Totzeit hingegen entfernt alle Ereignisse, die zu ihrem

Vorgänger einen kürzeren Abstand haben als die Totzeit. Allerdings mit

Nebenwirkungen, s.o.

Siehe auch:

http://www.strz.uni-giessen.de/ExpHelp/datarout/datarout.html

http://www.strz.uni-giessen.de/ExpHelp/datarout/datarout.pdf

Nächste: 8-Kanal 12-Bit ADC, Vorige: Programmierbare Totzeit, Nach oben: Standard-Interface-Karten [Inhalt]

| • Aufgabe, Funktion | ||

| • Bedienelemente | ||

| • Programmierung |

Nächste: Bedienelemente (CAN), Nach oben: CAN Controller [Inhalt]

Der CAN-Bus (Controller Area Network) wurde von Bosch entwickelt zur

Datenerfassung und Steuerung in Automobilen. Auf Grund der

außerordentlichen Fehlertoleranz des CAN-Protokolls

(Hamming Distanz = 6) sowie seiner Fähigkeit zur Selbstarbitrierung

und seiner Multi-Master-Fähigkeit

eignet er sich auch hervorragend zum Einsatz bei Experimenten und wird inzwischen gelegentlich auch dazu verwendet.

Details findet man z.B. unter:

http://www.can.bosch.com

http://www.mjschofield.com

Die CAN-Controller-Karte ist ein Interface zwischen dem Routing-Bus und dem CAN-Bus unter Verwendung des CC770 CAN-Controller-Bausteins von Bosch. Die Steuerung erfolgt über einen programierbaren ispLSI1032E Logikbaustein. Für die Initialisierungsdaten enthält die Karte einen EPROM.

Die CAN-Controller-Karte ist nicht galvanisch getrennt vom CAN-Bus, was zur Folge hat, dass alle am CAN-Bus angeschlossenen Einheiten eine solche galvanische Trennung haben sollten, falls sie nicht am gleichen 220V Netz angeschlossen sind und sich nicht räumlich dicht beieinander befinden.

Der CAN-Bus muss an beiden Enden mit 120 Ohm abgeschlossen sein. Auf der CAN-Controller-Karte kann mittels Jumper ein solcher Abschlusswiderstand aktiviert werden, was aber nur sinnvoll ist, wenn die Karte am Ende des Busses angeschlossen ist!

Nachdem die Karte mit Spannung versorgt ist, initialisieren sich zunächst die ispLSI1032E und CC770 Bausteine, danach werden die EPROM-Daten zum CC770 CAN-Controller übertragen. Das initialisieren des CC770 mit den EPROM-Daten kann auch jederzeit mit einen Init-Befehl durch die Software erfolgen. Danach kann die Software die vorausgegangene Initialisierung beliebig ändern, um eine passende Konfiguration zu erhalten. Die Initialisierung kann auch vollstd̈ig durch Software erfolgen, ein EPROM muss dann nicht vorhanden sein.

Die CAN-Controller-Karte belegt zwei Registeradressen des Address-Decoders (Siehe Address-Decoder.).

Nächste: Programmierung (CAN), Vorige: Funktion (CAN), Nach oben: CAN Controller [Inhalt]

| LED "Select": | leuchtet, wenn eines der zwei Register adressiert wird | |

| 9-pol. DSUB-Stecker: | Anschlussstecker für den CAN-Bus | |

| on Board Jumper: | Option für den CAN-Bus-Abschlusswiderstand |

Vorige: Bedienelemente (CAN), Nach oben: CAN Controller [Inhalt]

Überblick:

Register 0 out: Control/Mode/Address output

Bit 15 == 0 Control output

Bit 14 Reset command

Bit 13 Init command

Bit 15 == 1 Mode/Address output

Bits 11..08 Mode register

Bits 07..00 Address register

Register 0 in: Status input

Bit 14 Reset command activ

Bit 13 Init command activ

Bit 07 Controller busy

Bit 06 Interrupt flag

Bit 03 Error flag

Register 1 in/out: Data Register

Bits 07..00 8 bit data transfer

Bits 15..00 16 bit data transfer (project)

Mode-Register:

0 1 x--- read data write data direction of data transfer -x-- 8 bit data (16 bit data) currently only 8 bit transfers --x- fixed addr incr. addr address auto increment ---x not used not used

Address-Register:

Der CC770 CAN-Controller von Bosch hat 256 adressierbare Register,

deren Funktion in der CC770 Anleitung zu finden ist:

http://www.can.bosch.com/docu/InternetSpecification_CC770.pdf

oder InternetSpecification_CC770.pdf.

Für einen Datentransfer mit einem dieser Register des CC770 ist zuerst

das Adressregister der CAN-Controller-Karte mit der gewünschten

CC770-Registeradresse zu laden. Im Modus Address-Inkrement wird das

Adressregister nach jedem Datentransfer um eins erhöht, um fortlaufende

Daten ohne neue Adressierung lesen zu können.

Command-Register:

Status-Register:

Nächste: Standalone DAC-Boards, Vorige: CAN Controller, Nach oben: Standard-Interface-Karten [Inhalt]

| • Aufgabe, Funktion | ||

| • Bedienelemente | ||

| • Programmierung | ||

| • Analoge Bauteile |

Nächste: Bedienelemente (ADC8), Nach oben: 8-Kanal 12-Bit ADC [Inhalt]

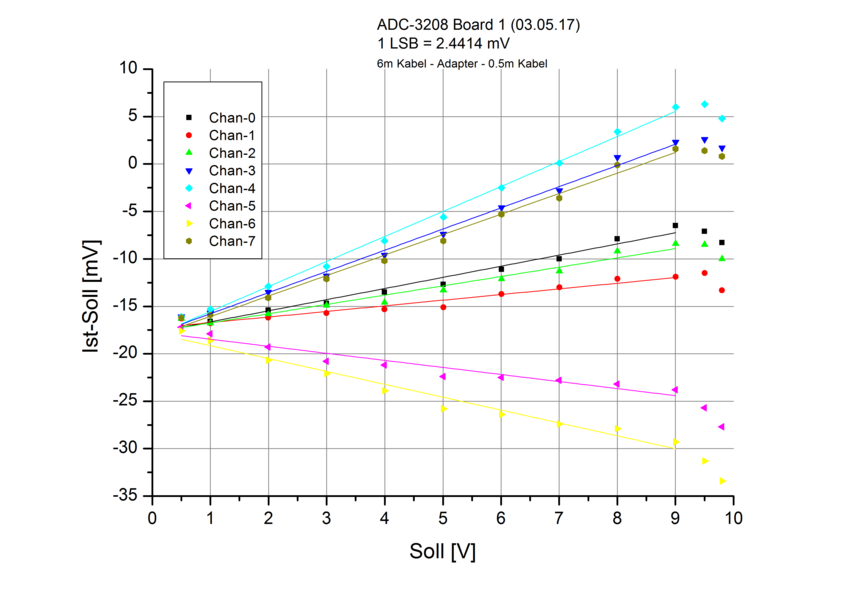

Die 8-Kanal 12-Bit ADC-Karte wurde entwickelt um die Plattenströme der neuen Elektronenkanone in Labor 017 zu überwachen.

Kanal ADC-Board Sensor-Einschub

+ - + -

0 1 2 1 14

1 3 4 2 15

2 5 6 3 16

3 7 8 4 17

4 9 10 5 18

5 11 12 6 19

6 14 15 7 20

7 16 17 8 21

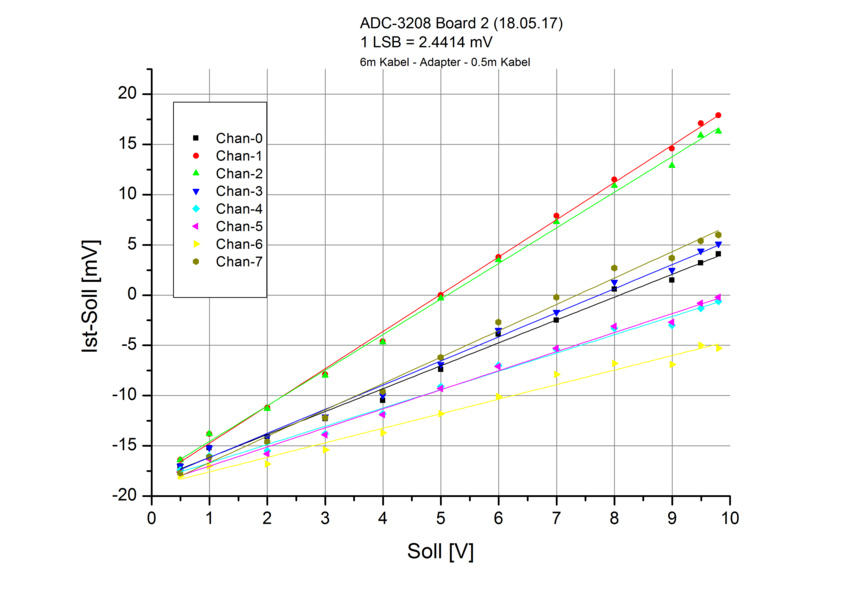

Ergebnisse eines linearen Fits von 0.5V bis 9V Sollwert für die ADC-Kanäle 0 bis 7.

Gleichung y = A + B*x [mV]

ADC-Board1 ADC-Board2

A0 -20.9 +- 0.3 -21.7 +- 0.4

B0 2.31 +- 0.05 3.15 +- 0.07

A1 -21.5 +- 0.4 -21.5 +- 0.4

B1 0.79 +- 0.08 3.66 +- 0.08

A2 -21.6 +- 0.4 -21.7 +- 0.3

B2 2.13 +- 0.07 4.56 +- 0.05

A3 -21.5 +- 0.4 -21.4 +- 0.3

B3 3.30 +- 0.07 3.37 +- 0.05

A4 -21.5 +- 0.4 -22.3 +- 0.2

B4 3.68 +- 0.07 2.83 +- 0.04

A5 -22.2 +- 0.4 -22.1 +- 0.3

B5 0.46 +- 0.08 2.78 +- 0.05

A6 -21.7 +- 0.4 -22.5 +- 0.4

B6 -0.26 +- 0.07 2.30 +- 0.07

A7 -22.2 +- 0.2 -23.5 +- 0.4

B7 3.21 +- 0.04 3.63 +- 0.07

A0 -17.81631 +- 0.36094

B0 1.17450 +- 0.06755

A1 -17.31443 +- 0.26169

B1 0.59412 +- 0.04897

A2 -17.73253 +- 0.35248

B2 0.98035 +- 0.06596

A3 -18.01110 +- 0.33027

B3 2.23223 +- 0.06181

A4 -18.16802 +- 0.30115

B4 2.63357 +- 0.05636

A5 -17.72569 +- 0.41256

B5 -0.74348 +- 0.07721

A6 -17.79580 +- 0.4471

B6 -1.35637 +- 0.08367

A7 -18.22818 +- 0.37118

B7 2.15909 +- 0.06946

A0 -17.81631 +- 0.36094 -18.42244 +- 0.39507

B0 1.17450 +- 0.06755 2.27836 +- 0.06305

A1 -17.31443 +- 0.26169 -18.43301 +- 0.29590

B1 0.59412 +- 0.04897 3.70690 +- 0.04722

A2 -17.73253 +- 0.35248 -18.09811 +- 0.33390

B2 0.98035 +- 0.06596 3.54296 +- 0.05328

A3 -18.01110 +- 0.33027 -18.55780 +- 0.36544

B3 2.23223 +- 0.06181 2.40070 +- 0.05832

A4 -18.16802 +- 0.30115 -18.51179 +- 0.33983

B4 2.63357 +- 0.05636 1.82093 +- 0.05423

A5 -17.72569 +- 0.41256 -18.90742 +- 0.33075

B5 -0.74348 +- 0.07721 1.89731 +- 0.05278

A6 -17.79580 +- 0.44710 -19.03359 +- 0.36677

B6 -1.35637 +- 0.08367 1.44670 +- 0.05853

A7 -18.22818 +- 0.37118 -19.29849 +- 0.39532

B7 2.15909 +- 0.06946 2.62594 +- 0.06309

Nächste: Programmierung (ADC8), Vorige: Funktion (ADC8), Nach oben: 8-Kanal 12-Bit ADC [Inhalt]

LED "Busy " : Anzeige einer Schreiboperation TP : Testpunkt zur Ausgabe von internen Signalen des ispLSI1032E

Nächste: Bauteile (ADC8), Vorige: Bedienelemente (ADC8), Nach oben: 8-Kanal 12-Bit ADC [Inhalt]

Die MCP3208-Karte belegt eine Control-Routing-Adresse für Ein/Ausgabe (Siehe Address-Decoder.). Mit der Ausgabe der ADC-Kanalnummer startet der ADC die Konvertierung des Analogsignals des angegebenen Kanals. Die Konvertierung benötigt 19 * 600ns = 11400ns. Während dieser Zeit wird das Acknowledge-Signal (AddAcc) für die Adressierung unterdrückt und erneute ADC-Starts werden ignoriert. Eingaben während dieser Konvertierungsphase liefern ungültige Werte und haben als Kennung das höchstwertige Bit gesetzt (0x8xxx). Dies könnte neben der Abfrage des AddAcc-Signals ebenfalls zur Synchronisierung mit dem ADC genutzt werden, es hat sich jedoch gezeigt, dass eine solche Eingabeoperation auf der Analogseite zu einer erheblichen Störung führt (ca. 30mV Schwankungen im Ergebnis). Nach der Konvertierungsphase kann das 12-bit Ergebnis beliebig oft mit einem Eingabebefehl abgerufen bzw. eine neue Konvertierung gestartet werden.

Zur Synchronisation mit dem ADC stehen zwei Statusabfragen zur Verfügung. Die Abfrage des Routing Status ist die bessere Variante da eine Dateneingabe mit Prüfung des Statusbits auf der ADC-Karte zu einer digitalen Störung führt!

Register Ausgabe: Ausgabe der Kanalnummer

Bits 15..04 0

Bits 03..00 Kanalnummer 0-7

Register Eingabe: Status/ADC-Daten Eingabe

Bit 15 == 1 ADC busy, Daten ungültig

Bit 15 == 0 ADC ready, Daten gültig

Bits 11..00 ADC Daten

Routing Status Eingabe:

(Routing Status & 0x0008) != 0 -> ADC busy, Daten ungültig

Diese Statusabfrage ist nur bei Verwendung einer neuen

Address-Decoder-Karte (EW 3/04) möglich da die alten

ebenfalls dieses Bit bedienen.

(Siehe Address-Decoder.)

Vorige: Programmierung (ADC8), Nach oben: 8-Kanal 12-Bit ADC [Inhalt]

Die acht Eingänge sind mit dem AD620B Instrumentation Amplifier bestückt:

Typ Max Nonlinearity 10 95 ppm Gain Error 0.10 0.15 % Input Offset 15 50 uV Output Offset 200 500 uV

Die Konvertierung erfolgt mit einem 12-bit, 8-Kanal ADC MCP3208B:

Typ Max Integral Nonlinearity +-0.75 +-1 LSB Diffenrential Nonlinearity +-0.5 +-1 LSB Offset Error +-1.25 +-3 LSB Gain Error +-1.25 +-5 LSB ( 1 LSB = 2.4414 mV)

Vorige: 8-Kanal 12-Bit ADC, Nach oben: Standard-Interface-Karten [Inhalt]

Die dual 16/18-Bit DAC-Karten wurde entwickelt zur Steuerung der Spannungen der verschiedenen Platten der neuen Elektronenkanone in Labor 017. Sie sind keine Control-Routing-Boards und gehören deshalb eigentlich nicht in diese Abteilung der Hardware-Beschreibungen.

Es existieren drei Varianten dieser DACs mit unterschiedlichen Eigenschaften, die sich jedoch alle bezüglich der Programmierung im Rahmen ihrer Möglichkeiten gleich verhalten. Bei den 16 Bit-DACs kommen die zwei niederwertigsten Bits nicht zur Anwendung:

Alle drei DAC-Karten besitzen ein eigenes Netzteil und benötigen nur 230V AC zu ihrem Betrieb. Die Spannungszuführung und Signalabführung erfolgen über eine Steckerleiste in den DAC-Boxen zu deren Rückseite. Die LTC-Karten haben zusätzlich einen dreipoligen Stecker zur Spannungszuführung und 2 * 2 Steckerstifte für die Signale auf dem Board als Einbauversion.

Die DAC-Karten werden über Lichtleiter angesteuert und sind deshalb für einen Betrieb auf höherem Potential geeignet. Als passender Lichtleitersender wurde das PSO14-Control-Routing-Board mit Firmware PSO32 (Siehe Serielle Ausgabe (PSO14).) entwickelt. Die Datenübertragung benötigt ca. 19us.

Die Ausgänge der DACs sind potentialfrei, deshalb ist Folgendes zu beachten:

Pin Signal 1 Out 2 Schutzerde 3 Masse

Die DAC-Karten sollten vorzugsweise ganz in der Nähe der zu steuernden Hochspannungsnetzgeräte platziert werden damit nur eine kurze Leitungslänge für die analogen Steuersignale benötigt wird.

| • Probleme und Lösungen | ||

| • DAC2752/2758-16/18-PSO32 | ||

| • DAC5541-16-pso32 |

Nächste: DAC2752/2758-16/18-PSO32, Nach oben: Standalone DAC-Boards [Inhalt]

Durchlaufverzögerung des LWL-Empfängers SFH551V

Der SFH551V ist relativ zum Bit-Takt (400ns) ziemlich lahm.

Insbesondere störend für das Timing sind die unterschiedlichen

Durchlaufverzögerungen für Licht-an und Licht-aus, die zu einer

Verkürzung des elektrischen Licht-aus Signals um bis zu max.

150ns führen, je nach Intensität des LWL-Signals und Temperatur.

Hinzu kommen noch 50ns Unschärfe durch das Einsychronisieren

auf den internen Clock-Takt (20MHz).

Das Timing kann bis auf 200ns verkürzte Bits sicher erkennen,

gemessen am Ausgang des SFH551V. Im Zweifel hilft ein längeres

LWL-Kabel.

Auf einer PSO14-Karte musste ein LWL-Sender ausgetauscht werden

da er zu hell war und den SFH551V völlig übersteuerte.

Nächste: DAC5541-16-pso32, Vorige: Probleme und Loesungen (DACx), Nach oben: Standalone DAC-Boards [Inhalt]

| • Funktion (DAC2752/2758) | ||

| • Bedienelemente (DAC2752/2758) | ||

| • Programmierung (DAC2752/2758) | ||

| • Probleme und Lösungen (DAC2752/2758) | ||

| • Anwendung bei der Elektronenkanone (DAC2752/2758) |

Nächste: Bedienelemente (DAC2752/2758), Nach oben: DAC2752/2758-16/18-PSO32 [Inhalt]

Zum Einsatz kommen sogn. Demo-Boards DC1684A mit den DACs LTC2752 (16 Bits) bzw. LTC2758 (18 Bits), die auf eine Europakarte mit Netzteil, LWL-Empfänger, Offset-/Gain-Abgleich und einem FPGA zur Steuerung montiert sind.

Nächste: Programmierung (DAC2752/2758), Vorige: Funktion (DAC2752/2758), Nach oben: DAC2752/2758-16/18-PSO32 [Inhalt]

Weitere Infos siehe: DEMO MANUAL DC1684A und LTC2752/LTC2758 Data Sheets

Manuelle Einstellung des Spannungsbereichs auf dem DC1684A-Board

Jumper MSPAN

0 programmierte Einstellung, beide DACs getrennt

1 manuelle Einstellung mittels Sn, beide DACs gemeinsam

Jumpers S2 S1 S0

0 0 0 0V to 5V

0 0 1 0V to 10V

0 1 0 -5V to 5V

0 1 1 -10V to 10V

1 0 0 -2.5V to 2.5V

1 0 1 -2.5V to 7.5V

Offset und Gain Abgleich

Mittels vier Potis können, falls nötig, Offset und Gain abgeglichen

werden wenn die zugehörigen Jumper auf EXT gesetzt sind:

Jumper Poti

Offset-A VOSADJA ?

Gain-A GEADJA ?

Offset-B VOSADJB ?

Gain-B GEADJB ?

Weitere Jumpers mit fester Einstellung

Jumper Position VREFA 5V Referenzspannungsquelle DAC-A VREFB 5V Referenzspannungsquelle DAC-B VCC REF 5V Spannungsquelle !CLR 1 Asynchrones Clear !LDAC 1 Asynchrones Load !RFLAG 1 Reset Flag Output

Anschlüsse und Testpunkte

LWL-Buchse : Lichtleiterempfänger DACA Stecker OUTA: Kanal A analoges Ausgangssignal DACA Stecker GNDA: Kanal A analoge Masse DACB Stecker OUTB: Kanal B analoges Ausgangssignal DACB Stecker GNDB: Kanal B analoge Masse TP 0 : Serielle LWL Daten TP 1 : Serielle DAC Daten TP 2 : DAC Chip Select TP 3 : DAC Clock 230 V Netzspannung an Steckerleiste VG32AC: 24 a,c Nullleiter 28 a,c 230V Leiter 32 a,c Schutzleiter 230 V Netzspannung an Stecker: ??? Nullleiter ??? 230V Leiter ??? Schutzleiter

Nächste: Probleme und Loesungen (DAC2752/2758), Vorige: Bedienelemente (DAC2752/2758), Nach oben: DAC2752/2758-16/18-PSO32 [Inhalt]

Die DAC2752/2758-Karten erhalten ihre Daten über Lichtleiter. Ein geeigneter LWL-Sender ist die PSO14-Karte mit Firmware PSO32 (Siehe Serielle Ausgabe (PSO14).).

Das Format der DAC-Daten ist das gleiche für die DAC2752- und

DAC2758-Karten. Für die DAC2752-Karten werden die beiden niederwertigsten

Bits jedoch nicht verwertet. Die Read Back Funktion der DACs wird nicht

unterstützt.

Bit-Folge, MSB zuerst:

4 Bit DAC-Kommando

0 0 1 0 Write Span DACn

0 0 1 1 Write Code DACn

0 1 0 0 Update DACn

0 1 0 1 Update all DACs

0 1 1 0 Write Span DACn, Update DACn

0 1 1 1 Write Code DACn, Update DACn

4 Bit DAC-Adresse

0 0 0 x DACA

0 0 1 x DACB

1 1 1 x all DACs

Danach folgt der DAC-Code bzw. der Span-Code, MSB zuerst:

18 Bit DAC-Code / 12 Bit don't care

6 Bit don't care / 04 Bit Span-Code

/ 8 Bit don't care

Nächste: Anwendungen (DAC2752/2758), Vorige: Programmierung (DAC2752/2758), Nach oben: DAC2752/2758-16/18-PSO32 [Inhalt]

Einschwingverhalten

Das Einschwingen erfolgt exponentiell mit folgenden Halbwertszeiten:

Bereich [V] 0 - 5 0 - 10 DAC2752 200ns 500ns DAC2758 150ns 250ns

Verhalten beim An-/Abschalten der DAC-Karten

Beim Anschalten der DAC-Karten pendelt die Ausgangsspannung, vermutlich

abhängig von dem Verhalten der Spannungsversorgung, zwischen erheblichen

positiven und negativen Werten.

Verhalten bei dem HAMEG HM8040-2 Triple Power Supply:

DAC2752 DAC2758

1ms -0.5V 1ms -2V

50ms 0->4V 0.1ms 1V

0.5ms 6V 50ms -0.5->0V

1ms 3V

Störungen durch das Schaltnetzteil

Die Messungen wurden als Differenzmessung mit zwei Tastköpfen

durchgeführt. Dabei ist das Ergebnis abhängig von der

Tastkopferdung. Bei den Messungen am Ausgang der DAC-Boxen waren die

Störungen z.B. deutlich geringer wenn beide Tastkopferdungen mit der

Schutzerde der Box verbunden waren.

Für die verbauten Morsun Schaltnetzteile wird Ripple & Noise mit max. 100mVss im Datenblatt angegeben. Tatsächlich wurde auf den Morsun-Ausgängen eine gedämpfte Hf-Störung (~2MHz, ~150mVss) im Takt der Schaltfrequenz (T~7/14us) angeregt, die auch genau so auf den DAC-Ausgängen zu beobachten war.

Mit folgenden Änderungen konnte die Hf-Störung für die DAC2752/2758 erheblich reduziert werden:

Mit diesen Maßnahmen lässt sich die Hf-Störung auf einen durch den Schaltvorgang hervorgerufenen low/high-Zacken (je 100ns) von 10mVss reduzieren. Dazwischen ca. 5mVss Restwelligkeit.

Bei Betrieb der Karte in einer der DAC-Boxen erhält man am Diodenstecker das gleiche Ergebnis. Allerdings erst nach Umlöten der falsch gepolten Netzfilter (Line - Load vertauscht). Alle Karten in der Box haben ein gemeinsames Netzfilter.

Vorige: Probleme und Loesungen (DAC2752/2758), Nach oben: DAC2752/2758-16/18-PSO32 [Inhalt]

Anschluss FUG

Getestet wurde mit dem alten, 1.5kV FUG (Plus-Pol geerdet).

!!!Achtung: mit geerdetem Minus-Pol liegen die

DAC-Anschlüsse auf Plus-HV-Potential!!!

Der Anschluss erfolgte von einer DAC-Box über 1.5m geschirmtes Kabel.

Die Schirmung war mit der Schutzerde der DAC-Box verbunden und hatte

keine Verbindung mit dem FUG.

Gemessen am FUG-Eingang treten gedämpfte Schwingungen auf:

100mVss, 10MHz

Mit 150nF oder galvanischer Verbindung zwischen Masse und Schutzerde am zur Karte gehörenden Nachbar-Ausgang der DAC-Box reduziert sich die Störung:

50mVss, 10MHz

Diese HF-Störung wirkt sich nur unwesentlich auf den FUG-Ausgang aus:

off 0 14 [V] FUG HV

10 10 10 [mVss] Rauschen

0 40 40 [mVss] HF Spitzen, weniger wenn DAC off

0 20 20 [mVss] 50Hz Brumm

Anschluss Kathodenregelung

Über die beiden DACs einer im Regeleinschub eingebauten DAC-Karte

wird der Sollwert (grob/fein) vorgegeben. Den Istwert erzeugt ein 1/400

HV-Teiler aus der FUG-Hochspannung. Ein Integralregler liefert den

Stellwert für das Kepco. Das Kepco gibt die Vorspannung für das FUG.

Durch die Regelung wird der 50Hz Brumm des alten FUG auf <10mVss reduziert. Im Takt der 50Hz Halbwellen ist jedoch für 5ms eine andauernde HF-Störung zu sehen.

Folgendes wurde untersucht um die Ursache der Störung zu finden:

Folgendes wurde zur Reduzierung der Störungen unternommen, gemessen am HV-Eingang der Regelung:

FUG: 0V, Kepco: 25V - 0V Rauschen Brumm HF Spitzen [mVss] 10 10 - 20 FUG-DAC off

FUG: 14V, Kepco: 25V - 14V Rauschen Brumm HF Spitzen [mVss] 10 10 40 50 FUG-DAC on, 10 10 <10 20 FUG-DAC on, 150nF am Nachbarausgang

50Hz-Brumm an KEPCO Ausgang:

Die DAC-Ausgänge haben je nach dem wo sie positioniert sind einen geringen

Brummanteil (<5mVss). Im Verbund mit der Kathodenspannungsregelung

(Spannungsteiler, Regelung, KEPCO) tritt jedoch zum Teil erheblicher Brumm

auf.

Alle Geräte abgeschaltet und Netzstecker von: Regelung aus ein ein ein ein ein ein KEPCO aus aus ein aus ein ein gedreht FUG aus aus aus ein ein gedreht ein Brumm [mVss] 2 2 10 5 15 30 30

Alle Geräte eingeschaltet, 1/200 Teiler:

ohne Masseverbindung zwischen den Geräten: 60mVss

mit Masseverbindung zwischen Regelung und KEPCO: 60mVss

mit Masseverbindung zwischen Regelung und FUG

und spezieller Leitungsführung: 10mVss

Alle Geräte eingeschaltet, 1/1000 Teiler:

ohne Masseverbindung zwischen den Geräten: 600mVss

mit Masseverbindung zwischen Regelung und KEPCO: 1000mVss

mit Masseverbindung zwischen Regelung, Teiler, KEPCO: 80mVss

Lässt sich durch zusätzliche Verbindung vom

Deckel der Regelung zum Teiler noch reduzieren: 30mVss

mit Masseverbindung zwischen Regelung und FUG: 200mVss

mit Masseverbindung zwischen Regelung, Teiler, FUG: 200mVss

Vorige: DAC2752/2758-16/18-PSO32, Nach oben: Standalone DAC-Boards [Inhalt]

| • Funktion (DAC5541) | ||

| • Bedienelemente (DAC5541) | ||

| • Programmierung (DAC5541) | ||

| • Probleme und Lösungen (DAC5541) |

Nächste: Bedienelemente (DAC5541), Nach oben: DAC5541-16-pso32 [Inhalt]

Testdaten der DAC-Boards, Abweichungen vom Sollwert Sollwerte 0 1 2 4 6 8 9 10 V -------------------------------------------------- DAC1/0 -1 -2 -2 -2 -2 -2 -2 -2 mV DAC1/1 -1 -2 -2 -2 -2 -2 -2 -2 mV DAC2/0 0 0 0 0 0 0 0 0 mV DAC2/1 +2 +2 +2 +2 +2 +2 +2 +2 mV DAC3/0 +2 +2 +2 +2 +2 +2 +2 +2 mV DAC3/1 0 0 0 0 0 0 0 0 mV DAC4/0 1 0 1 0 0 0 0 -1 mV DAC4/1 1 1 1 0 0 0 -1 -1 mV DAC5/0 0 -1 -1 -1 -1 -1 -1 -1 mV DAC5/1 0 0 0 0 0 0 0 0 mV

Typ Max Relative Accuracy +-0.5 +-1 LSB Diffenrential Nonlinearity +-0.5 +-1 LSB Zero Code Error +-0.3 +-0.7 LSB Gain Error +-0.5 +-2 LSB Voltage Settling Time 1 us ( 1 LSB = 0.15259 mV)

Typ Max Offset 0.5 3 mV Offset Drift 2 uV/K Output Current 15 mA

Nächste: Programmierung (DAC5541), Vorige: Funktion (DAC5541), Nach oben: DAC5541-16-pso32 [Inhalt]

Die Funktion einiger Bedienelemente hat sich im Laufe der Weiterentwicklung geändert. So war ursprünglich aus historischen Gründen für jeden Kanal eine eigene LWL-Verbindung vorgesehen, nun wird aber nur noch eine einzige benötigt, weshalb beide jetzt die gleiche Funktion haben. Ebenso haben die Testpunkte eine neue Funktion erhalten.

LWL-Buchse 0 : Lichtleiterempfänger Kanal 0 und 1 LWL-Buchse 1 : Lichtleiterempfänger Kanal 0 und 1 DAC0 Stecker OUT : Kanal 0 analoges Ausgangssignal DAC0 Stecker GNDA: Kanal 0 analoge Masse DAC1 Stecker OUT : Kanal 1 analoges Ausgangssignal DAC1 Stecker GNDA: Kanal 1 analoge Masse TP 0 word : Serielle LWL Daten TP 1 word : Serielle DAC Daten TP 0 bit : DAC Chip Select TP 1 bit : DAC Clock 230 V Netzspannung an Steckerleiste VG32AC: 24 a,c Nullleiter 28 a,c 230V Leiter 32 a,c Schutzleiter

Nächste: Probleme und Loesungen (DAC5541), Vorige: Bedienelemente (DAC5541), Nach oben: DAC5541-16-pso32 [Inhalt]

Die DAC5541-Karte erhält ihre Daten über Lichtleiter. Ein geeigneter LWL-Sender ist die PSO14-Karte mit Firmware PSO32 (Siehe Serielle Ausgabe (PSO14).).

Das Format der DAC-Daten ist das gleiche wie für die DAC2752- und DAC2758-Karten, es kann jedoch nur eine Untermenge der Kommandos ausgeführt werden:

4 Bit DAC-Kommando

nur für die Bit-Muster (0 x 1 1) erhält der DAC5541 neue Daten

4 Bit DAC-Adresse

x 0 0 x DAC0

x 0 1 x DAC1

x 1 1 x DAC0 und DAC1

18 Bit DAC-Daten, MSB zuerst

6 Bit nicht genutzt

Vorige: Programmierung (DAC5541), Nach oben: DAC5541-16-pso32 [Inhalt]

Einschwingverhalten

Laut Datenblatt sollten die DACs in ca. 2 us ihren Endwert erreichen.

Im Test zeigte sich jedoch, dass sie zunächst ca. 10% überschwingen

(auch zu negativen Werten!)

um sich dann mit einer Halbwertszeit von ca. 50us exponentiell dem

Sollwert zu nähern (Ursache unklar).

Dieses Überschwingen konnte kompensiert werden durch

1.5nF * 30KOhm = 45us in der Rückkopplung des AD820. Die Halbwertszeit

reduzierte sich damit auf ca. 25us. Nach 250us ist die Abweichung vom

Sollwert also nur noch 0.0001.

Verhalten beim An-/Abschalten der DAC-Karte

Beim Anschalten der DAC-Karte sollte der AD5541CR laut Datenblatt

einen Reset durchführen. Möglicherweise klappt dies in seltenen

Fällen nicht immer.

Beim Abschalten der DAC-Karte geht der Ausgang kurzzeitig zu negativen

Werten (ca. -5V) um nach ca. 400ms 0V zu erreichen. Mit einer Diode

am Ausgang können diese negativen Werten auf -0.6V/200ms begrenzt werden.

Eine gute Idee ist auch, dafür zu sorgen, dass die DACs immer nur

gemeinsam mit den Hochspannungsgeräten abgeschaltet werden.

Störungen durch das Schaltnetzteil

Die DAC5541-Karten werden ebenfalls durch das Schaltnetzteil stark

gestört. Gegenmaßnahmen wie bei den DAC2752/2758-Karten wurden

bisher noch nicht untersucht.

Nächste: Zaehlratenstatistik, Vorige: Standard-Interface-Karten, Nach oben: Top [Inhalt]

An dieser Stelle sind Interface-Karten verzeichnet, die nur als Einzelexemplare für ein spezielles Labor/Experiment entwickelt wurden. Details findet man möglicherweise in den Unterlagen der zugehörigen Experimente. Diese Aufstellung enthält auch Oldies, in der Hoffnung, sie eines Tages wieder recyclen zu können.

| • Schrittmotor-Interface (Labor 016) | ||

| • Probenwechsler-Steuerung (Schacht) |

Nächste: Probenwechsler-Steuerung, Nach oben: Spezielle Interface-Karten [Inhalt]

| • Aufgabe, Funktion | ||

| • Bedienelemente | ||

| • Programmierung |

Nächste: Bedienelemente (SMI), Nach oben: Schrittmotor-Interface [Inhalt]

Interface zu einer Eigenbau-Schrittmotorsteuerung, mit der ein Schlitz durch die Strahlen gefahren wird zur Strahlprofilanalyse (IIF-Messprogramm).

Mit einem Befehl können maximal 65565 Schritte in vorwärts oder rückwärts Richtung ausgeführt werden. Die Schrittgeschwindigkeit wird von der Schrittmotorsteuerung vorgegeben.

Der Schrittmotor wird angehalten bei folgenden Ereignissen:

Das Schrittmotor-Interface belegt vier Registeradressen des Address-Decoders (Siehe Address-Decoder.).

Nächste: Programmierung (SMI), Vorige: Funktion (SMI), Nach oben: Schrittmotor-Interface [Inhalt]

Das Schrittmotor-Interface enthält nur einen 7-poligen Phonostecker zum Anschluss der Schrittmotor-Steuerung:

Pin Signal 1 !Schrittmotor online (in) 2 !Alarm Obergrenze (in) 3 !Alarm Untergrenze (in) 4 Schrittmotor-Takt (in) 5 !Start Motor (out) 6 !Hochlauf (out) 7 Masse

Vorige: Bedienelemente (SMI), Nach oben: Schrittmotor-Interface [Inhalt]

Register 0: Reset-Kommando (0 Bits)

Register 1 out: Anzahl der Schrittmotorschritte (16 Bits)

im 1-Komplement:

0 -> 0xff

1 -> 0xfe

Register 2 out: Start-Kommando, Richtung (1 Bit)

Bit 0 0 = Schlitz nach unten

Bit 0 1 = Schlitz nach oben

Register 3 in: Status-Eingabe

Bit 15 1 = Schrittmotor ist online

Bit 14 1 = Schlitz am oberen Limit

Bit 13 1 = Schlitz am unteren Limit

Bit 12 1 = busy, Schrittmotor läuft

Vorige: Schrittmotor-Interface, Nach oben: Spezielle Interface-Karten [Inhalt]

!!! unvollständig, mehr im Ordner "Probenwechsler" !!!

| • Aufgabe, Funktion | ||

| • Bedienelemente | ||

| • Programmierung | ||

| • Probenwechsler Details |

Nächste: Bedienelemente (PWS), Nach oben: Probenwechsler-Steuerung [Inhalt]

Die Probenwechsler-Steuerung besteht aus zwei Control-Routing-Karten. Sie wurde entwickelt zur Steuerung des Probenwechslers von H. Schacht (s.h. Diplomarbeit H. Schacht: Ein automatisierter Gamma-Messplatz für Photonenaktivierungsanalyse (1992)).

Der Probenwechsler transportiert mit Hilfe von 4 Schrittmotoren die Proben aus einem Magazin vor den Detektor und wieder zurück. Ein weiterer Motor bedient ein Eingangstor zur Bleiburg, in der gemessen wird. Über 9 Sensoren wird der Transport und der Status des Eingangstores überwacht.

Die Probenwechsler-Steuerung belegt sechs Registeradressen des Address-Decoders (Siehe Address-Decoder.).

Es existiert nur eine handverdrahtet Version der Karten.